Несколько лет назад мне довелось посетить университет Харви-Мадд, в котором работали Дэвид Харрис и Сара Харрис, авторы известного учебника "Цифровая схемотехника и архитектура компьютера". Cлучайно зашел в комнату, в которой сидела группа студентов и лежало нечто, напоминающее торпеду. Выяснилось, что это подводный робот, а студенты работают над общением этого робота с рыбами с помощью сонара (так я перевел для себя "IVER AUV for Sonar Mapping and Fish-Robot Interaction Modeling Projects"), и даже получили пару грантов на полмиллиона долларов.

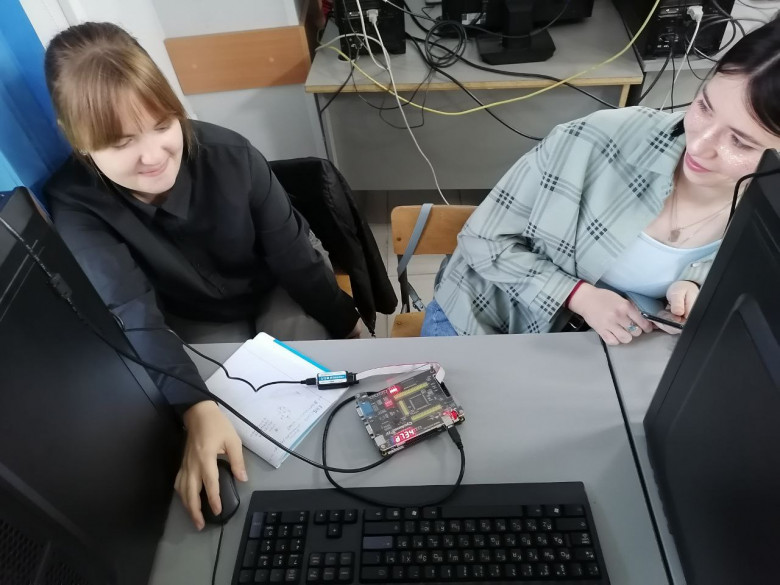

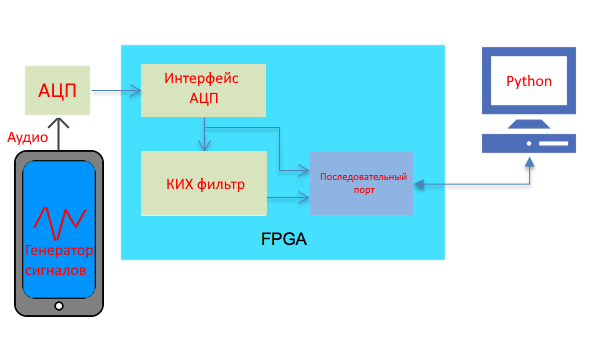

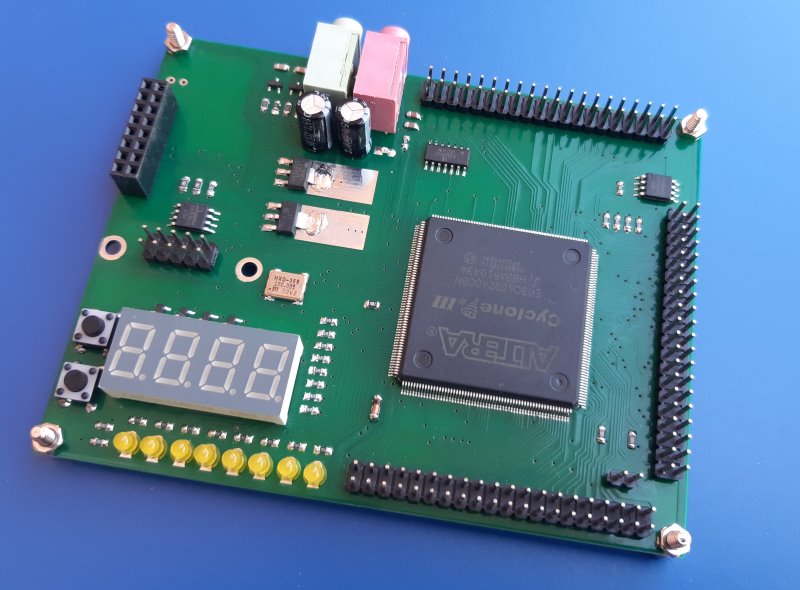

Но чтобы студенты могли сделать что-нибудь полезное в обработке сигнала от сонара, им нужно знать кучу математики из области, которая в Америке называется DSP, а в России - ЦОС, или Цифровая Обработка Сигналов. Потом, в своих поездках по России я выяснил, что российские студенты в ЦОС тоже не лыком шиты.