Комментарии 12

Спасибо за интересную статью.

Вопрос к вам, автор. Вы могли бы рассказать о том, в каких схемах обычно требуется избавиться от сбоев, и как это достигается? Исходя из моего скромного опыта разработок на FPGA, сбои присутствуют в логических схемах повсюду и спасает от них лишь синхронность работы устройства.

Вопрос к вам, автор. Вы могли бы рассказать о том, в каких схемах обычно требуется избавиться от сбоев, и как это достигается? Исходя из моего скромного опыта разработок на FPGA, сбои присутствуют в логических схемах повсюду и спасает от них лишь синхронность работы устройства.

+1

в каких схемах обычно требуется избавиться от сбоев

В безопасных системах автоматики и телемеханики, в медицине, в реакторных системах, в различных АСУ ТП.

как это достигается

Путем способности системы к переходу в предопределенное безопасное состояние в случае своего собственного отказа.

0

Путем повышения надежности за счет дублирования блоков структурных элементов схемы в сочетании с программной частью (если это MCU).

0

Ну здесь вопрос все таки был вполне конкретный про «сбои» логических функций, которые вовсе не сбои, а glitch, не помню хорошего русского термина.

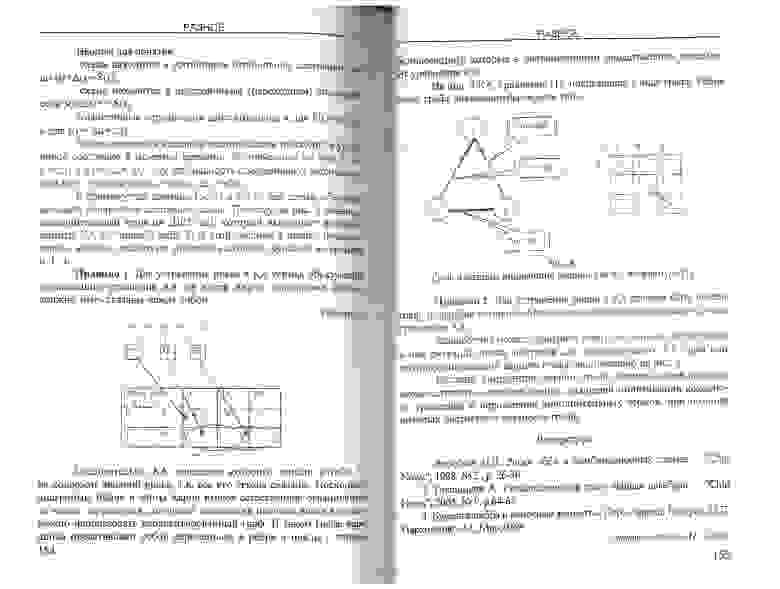

MichaelBorisov, чтобы их избежать, специальным образом модифицирую логическую функцию, не минимизируя ее полностью как только можно, а оставляя избыточной. По картам Карно это как-то очевидно делается, но за давностью лет уже не помню (на практике ни разу не пригодилось). Не уверен что для современных FPGA это вообще реализуемо, ввиду использования сложных базовых логических элементов (LUT), в отличии от элементарного базиса типа 2-И-НЕ.

MichaelBorisov, чтобы их избежать, специальным образом модифицирую логическую функцию, не минимизируя ее полностью как только можно, а оставляя избыточной. По картам Карно это как-то очевидно делается, но за давностью лет уже не помню (на практике ни разу не пригодилось). Не уверен что для современных FPGA это вообще реализуемо, ввиду использования сложных базовых логических элементов (LUT), в отличии от элементарного базиса типа 2-И-НЕ.

+2

Поздравляю с получением инвайта! Я знал, что у вас всё получится.

+1

Интересно, почему это называется «сбоем»? Это вполне характеризуемая величина, назовём её «время отклика» (или обратная величина, «предельная частота» работы схемы), то есть время проходящее между изменением входного воздействия и временем когда выходное состояние установится в соответствии с входным воздействием. Если входное воздействие изменяется быстрее, чем скорость срабатывания то, состояние выхода считается неопределённым.

Вообще говоря, в любой комбинационной цепи есть задержка. И даже задержка на двух одинаковых логических элементах «И» будет разная, даже если физически они расположены рядом и изготовлены по одной технологии. Средства проектирования FPGA/ASIC или печатных плат умеют считать задержки на элементах и соответственно выравнивать пути и размещение для уменьшения перекоса/разбежек и т.п. (все, наверное, на материнских платах видели змейки из дорожек — это обычный способ выровнять перекос фаз на разных сигналах одной шины).

Сбой в моём понимании — нечто случайное и, возможно, характеризуемое вероятностью. А в статье описан не сбой, это величина (точного названия не знаю, увы) которую можно и нужно учитывать.

Расскажите лучше про метастабильность, вот это похоже на сбой.

Вообще говоря, в любой комбинационной цепи есть задержка. И даже задержка на двух одинаковых логических элементах «И» будет разная, даже если физически они расположены рядом и изготовлены по одной технологии. Средства проектирования FPGA/ASIC или печатных плат умеют считать задержки на элементах и соответственно выравнивать пути и размещение для уменьшения перекоса/разбежек и т.п. (все, наверное, на материнских платах видели змейки из дорожек — это обычный способ выровнять перекос фаз на разных сигналах одной шины).

Сбой в моём понимании — нечто случайное и, возможно, характеризуемое вероятностью. А в статье описан не сбой, это величина (точного названия не знаю, увы) которую можно и нужно учитывать.

Расскажите лучше про метастабильность, вот это похоже на сбой.

0

Судя по всему, автор имел в виду английское слово «glitch», которое означает не нарушение работы схемы, а нормальное явление, происходящее при ее работе. Возможно, в русском языке здесь больше подойдет термин «выброс», а не «сбой».

А что до метастабильности — доказано, что не существует способа совсем избавиться от нее. В любой асинхронной схеме с D-триггерами поэтому метастабильность неизбежна. А раз так, то разработчикам схемы приходится ее учитывать и бороться с последствиями, предотвращая распространение метастабильности по схеме и нарушения тем самым ее нормальной работы.

А что до метастабильности — доказано, что не существует способа совсем избавиться от нее. В любой асинхронной схеме с D-триггерами поэтому метастабильность неизбежна. А раз так, то разработчикам схемы приходится ее учитывать и бороться с последствиями, предотвращая распространение метастабильности по схеме и нарушения тем самым ее нормальной работы.

0

Ребята, в топике я выдвинул еще одну идею — минимизация булевых функций посредством упрощения выражений. Кто занимается дискретной математикой, скажите, есть что-то подобное? Кстати, где-то читал, что «glitch» и «сбой» — это одно и то же. Оказывается, разные понятия, спасибо, буду знать. Я то сам не схемотехник, а математик.

0

Видеолекция по данной теме

0

Презентация с примером минимизации булевой функции (4-ый слайд).

0

Критика (статья в журнале «Радиопромышленность», 2010, №2, с. 152-155)

Статья в журнале

0

Зарегистрируйтесь на Хабре, чтобы оставить комментарий

Анализ цифровых схем на риски сбоя