Комментарии 6

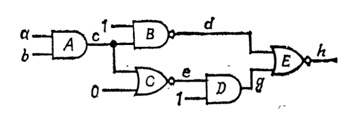

Замечу, что в отсутствие задержек на выходе h будет ровно то же самое, что и на c.

0

А что это меняет? Вся проблема в том, что задержки всегда есть. А они в свою очередь порождают всякие проблемы. Те же гонки данных/сигналов. И в этом смысле на примере схем хорошо изучать и демонстрировать проблемы параллельного программирования. Они же, кстати, служат хорошим тестом проверки на параллелизм того или иного языка, среды исполнения/моделирования и т.п.

0

Просто пример у японских авторов показался мне нереалистичным. Может быть, стоит сперва провести очевидные минимизации, а потом уже считать задержки. К тому же тут минимизация вообще смешная: выкидывание 80% вентилей.

Вы же ниже в комментариях приводите нормальный пример. Может быть, реализация какого-нибудь 2:1 MUX тоже подошла бы. Если что, я в задержках не силен, только в минимизации немного.

0

Похоже, японцы, действительно, схитрили. И, признаюсь, Вы заметили то, что теперь стало очевидно даже мне. Спасибо ;)

Конечно, по-хорошему нужна сначала минимизация. Здесь Вы абсолютно правы. А задержки будут, если после минимизации останется даже один элемент. Просто минимизация элементов приведет к минимизации задержек и, соответственно, к минимизации/исключению риска сбоя. Так что все связано.

А японцы — они японцы и есть. Они хитрые, а мы… дотошные :)

Но, еще раз, в данном случае все же не важна сама схема, а важно было показать (как японцам, так и мне) наличие проблем в схемах при распространении сигналов. И что эти проблемы будут даже у минимизированных схем. Особенно если после минимизации останется достаточное число элементов и будут гонки сигналов.

Конечно, по-хорошему нужна сначала минимизация. Здесь Вы абсолютно правы. А задержки будут, если после минимизации останется даже один элемент. Просто минимизация элементов приведет к минимизации задержек и, соответственно, к минимизации/исключению риска сбоя. Так что все связано.

А японцы — они японцы и есть. Они хитрые, а мы… дотошные :)

Но, еще раз, в данном случае все же не важна сама схема, а важно было показать (как японцам, так и мне) наличие проблем в схемах при распространении сигналов. И что эти проблемы будут даже у минимизированных схем. Особенно если после минимизации останется достаточное число элементов и будут гонки сигналов.

0

Выше в ПОХОЖИЕ ПУБЛИКАЦИИ ссылка на статью Анализ цифровых схем на риски сбоя.

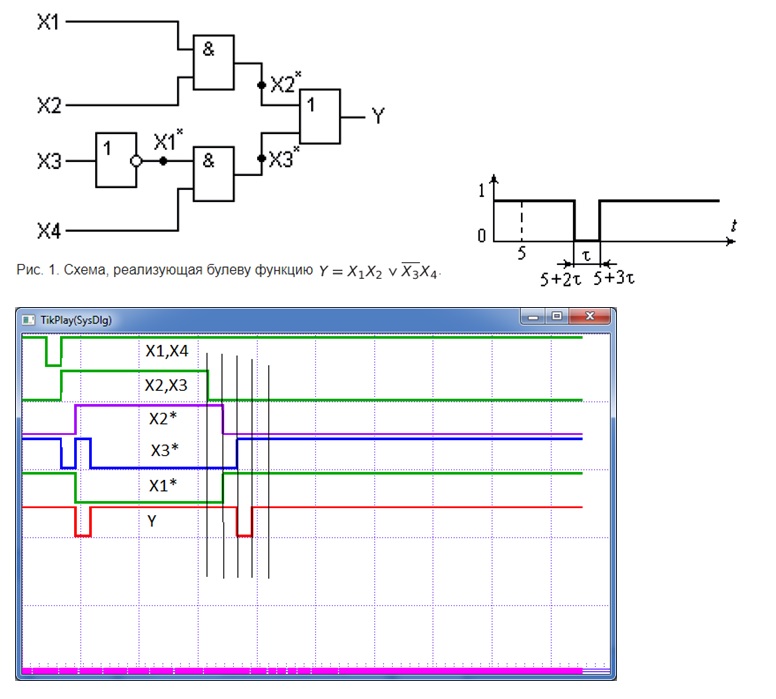

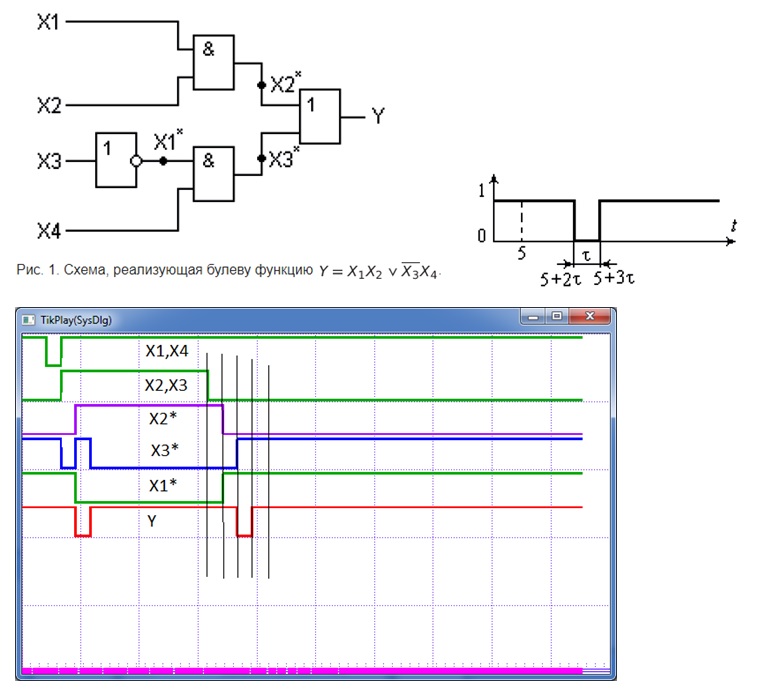

Я открыл и провел эксперимент. И вот, что получилось:

Результат как бы совпадает, но есть вопросы по диаграмме (по времени моделирования).

И дальше. Если последнему элементу увеличить задержку (на рис. все задержки единичные) и сделать ее инерционной, то риска сбоя на выходе схемы не будет.

А что будет, если всем элементам увеличить задержку?

А что будет, если все задержки сделать инерционными (это будет уже почти реальная схема)?

А если элементы будут иметь разные задержки?..

Поэтому иметь аналитическое решение — это, конечно, хорошо. Но ответит ли оно на все возникающие при исследовании схемы вопросы? Мне почему -то кажется, что нет…

Я открыл и провел эксперимент. И вот, что получилось:

Моделирование схемы из статьи

Результат как бы совпадает, но есть вопросы по диаграмме (по времени моделирования).

И дальше. Если последнему элементу увеличить задержку (на рис. все задержки единичные) и сделать ее инерционной, то риска сбоя на выходе схемы не будет.

А что будет, если всем элементам увеличить задержку?

А что будет, если все задержки сделать инерционными (это будет уже почти реальная схема)?

А если элементы будут иметь разные задержки?..

Поэтому иметь аналитическое решение — это, конечно, хорошо. Но ответит ли оно на все возникающие при исследовании схемы вопросы? Мне почему -то кажется, что нет…

+1

И еще прямо в тему :)

Вот сегодня пришло на почту: Реализация логических элементов с помощью нейронной сети на STM32F4

Интересное, конечно использование нейронных сетей. Но можно ли доверять такой сети, если она построена приведенной по таблице истинности. Ведь реальный элемент так не работает. Он имеет задержку, тип этой задержки инерционный…

Конечно, NN — это модно и современно. Но как бы нужно знать и видеть «берега»…

Или как?

Вот сегодня пришло на почту: Реализация логических элементов с помощью нейронной сети на STM32F4

Интересное, конечно использование нейронных сетей. Но можно ли доверять такой сети, если она построена приведенной по таблице истинности. Ведь реальный элемент так не работает. Он имеет задержку, тип этой задержки инерционный…

Конечно, NN — это модно и современно. Но как бы нужно знать и видеть «берега»…

Или как?

+1

Зарегистрируйтесь на Хабре, чтобы оставить комментарий

Реализация инерционных алгоритмов на примере логического моделирование цифровых схем