Предисловие

Идеей создания собственного простого процессора, если это можно так назвать, я загорелся давно. Выбор архитектуры — дело неодназаначное, но будучи от части минималистом, захотелось реализовать что-то простое, в то же время мощьное и расширяемое, TTA отлично для этого подошла.

Часть 1.

Часть 2.

Если вкратце, идея заключается в том, что-бы у блока управления была лишь одна команда перемещения данных, а вычисления являлись побочным продуктом этих перемещений.

Воплощать это в жизнь буду в простой программе для составления и симуляции логических и электрических схем — Logisim, выбрал её из-за простоты и доступности, в случае удачной реализации, планируется переписать на Verilog.

При чтении лучше сразу трогать проект, его можно найти в конце статьи.

Блок управления

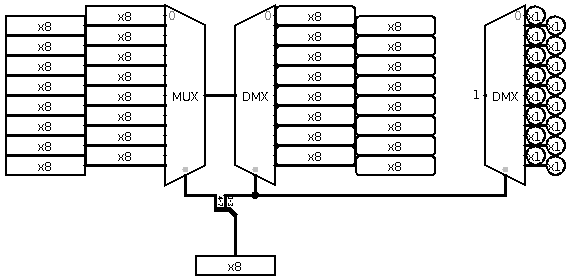

Блок управления — главная составляющая. Для простоты было решено выбрать 16 входов и 16 выходов, в итоге команда, поступающая в БУ получается 8-битная, первая половина которой указывает на один из входов, другая на один из выходов. Для того что-бы принимающий блок мог понять что к нему пришли данные, добавляется 1 бит на каждый вход из блока, принято эти блоки называть функциональными блоками.

Итак:

Память

Что-бы БУ мог исполнять программу, её надо где-то хранить, память будет представлять из себя функциональный блок, один из выходов который будет подключен к шине команд БУ.

Итак:

Самый нижний вход — тактовый сигнал, самый левый — входные данные, самый правый — выходные данные, они же команды БУ и последний — тот самый, служащий флагом, сообщающий о приходе данных. При получении данных, она записываются в счетчик, который указывает на текущюю команду, при каждом тактовом импульсе счетчик увеличивается, а БУ передает данные из одного ФУ в другое.

Другие простые ФУ

Создадим проcтые ФУ, которые будут выполнять банальные действия сложения и вычитания.

Шаблон ФУ выглядит так: на входе 8-битные регистры по количеству входов, запись в них осуществляется при поступлении данных. На выходе могут быть так-же регистры, в которых будет хранится ответ, но для сумматора это не обязательно.

Таким образом сумматор и вычитатель будет выглядеть так:

Готовое устройство

Давайте же соединим память и БУ, а после попробуем создать новое ФУ и написать программу.

В качестве тактового сигнала будет выступать кнопка.

Итак соединение:

Теперь подсоединим сумматор и вычитатель, а так-же две константы на вход:

Всё готово, чтобы написать программу, она будет выполнять банальную последовательность действий: прибавлять единицу к предыдущему значению сумматора, после чего переходить на начало посредством относительного перехода (для этого и был сделан вычитатель:3).

Напишем программу.

Изначально все регистры обнулены, поэтому делать это нет смысла, первой командой будет отправка единицы на один из вход сумматора (In3 -> O2), отправка выхода сумматора на его второй вход (In1 -> O1), оправка текущего адреса ячейки памяти на вход вычитателя (In0 -> O3), отправка изменения адреса на другой вход вычитателя, он будет вычитаться (In4 -> O4), после выход вычитателя на вход указателя адреса, тем самым выполнив переход(In2 -> O0).

Программа выглядит так:

1. In3 -> O2

2. In1 -> O1

3. In0 -> O3

4. In4 -> O4

5. In2 -> O0

В памяти:

Вот и всё. Эта программа исправно работает. Планирую сделать больше ФУ и сделать их соединение с БУ удобнее, кстати ФУ практически представляют собой ControlFlow устройства. Так же можно соединить несколько БУ вместе, то есть создать сеть таких устройств.

Спасибо за внимание!

→ GitHub