Комментарии 90

Хочу порекомендовать вот этот цикл статей:

www.kit-e.ru/articles/circuit/2008_3_161.php

Мне в свое время сильно помогло «въехать в тему»

www.kit-e.ru/articles/circuit/2008_3_161.php

Мне в свое время сильно помогло «въехать в тему»

+3

Поскольку автор собирает синтезатор, в первую очередь понадобится аудио-обвес. Можно сделать вывод и на gpio, но для чего-то мало-мальски серьёзного нужен внешний DAC. Ну и VGA всегда полезен, если его есть куда воткнуть, хотя бы для отладочной информации. Свитчей несколько чтоб было, остальное по вкусу.

0

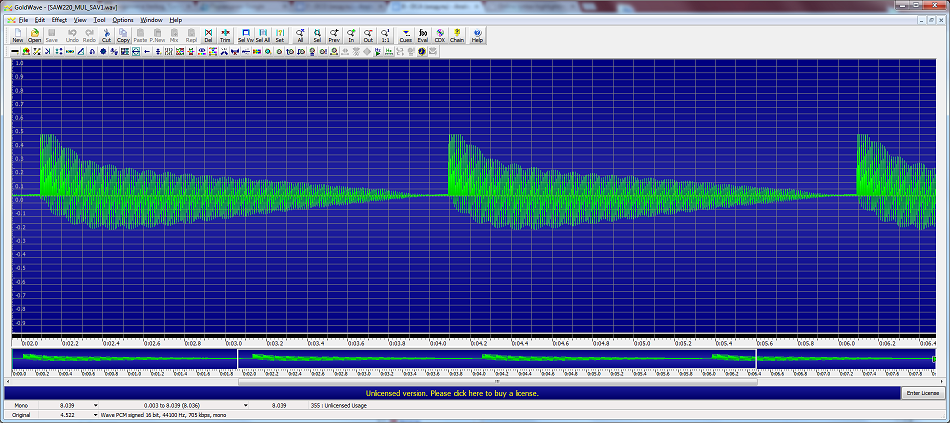

Для отладки вывод звука делаю пока так.

Преобразовываю либо ШИМ (8 бит), либо дельта-сигма (8-16 бит), по звуку даже более-менее приемлемо:

Хотя форма мне не очень нравится (асимметрия):

Преобразовываю либо ШИМ (8 бит), либо дельта-сигма (8-16 бит), по звуку даже более-менее приемлемо:

Хотя форма мне не очень нравится (асимметрия):

0

Я просто не привязываясь к конкретному проекту. У меня был тяжёлый но интересный старт с CPLD EPM7064, для которой сам паял макетку. И если что то шло не так то понять было не легко кто виноват, особенно учитывая частоты на которых может работать FPGA/CPLD. После покупки Terasic DE1 жить стало в разы легче, учитывая количество примеров идущих с платой.

+2

Уже который раз хочу собрать на FPGA хоть что-то, но каждый раз прихожу в уныние от того, что банально не хватает времени.

Свой проект двигается, но медленно… а хочется схватиться за всё… \Иногда, правда, в ответ получается удар током, но тут уже куда деваться\

Например, хочется добить декодер HDB3 (E1) с его экспресс-анализом и выводом в контроллер и передачей куда-нибудь дальше для логгирования. Что останавливает? Теперь -1 к количеству причин!

Свой проект двигается, но медленно… а хочется схватиться за всё… \Иногда, правда, в ответ получается удар током, но тут уже куда деваться\

Например, хочется добить декодер HDB3 (E1) с его экспресс-анализом и выводом в контроллер и передачей куда-нибудь дальше для логгирования. Что останавливает? Теперь -1 к количеству причин!

+1

У вас интересный проект, но видно, что он почти на грани для МК. В нем больше борьбы с МК, чем с задачей. А может стоит попробовать решить на ПЛИС? Кстати мы сейчас «раскуриваем» модуль для DHT22. А пример работы с ds18b20 уже есть. И поставить их можно будет столько, сколько нужно.

Однако, есть чему и поучиться, например теме с 74HC595 по расширению количества ног. Я тут про эту микросхему как раз вспоминал недавно. Может показаться странным, но есть у меня на примете задачи, где даже ~80 ног ПЛИС на ввод/вывод будет не достаточно :) Кстати, раз уж вы в курсе дела, до каких частот работает эта микросхема?

Однако, есть чему и поучиться, например теме с 74HC595 по расширению количества ног. Я тут про эту микросхему как раз вспоминал недавно. Может показаться странным, но есть у меня на примете задачи, где даже ~80 ног ПЛИС на ввод/вывод будет не достаточно :) Кстати, раз уж вы в курсе дела, до каких частот работает эта микросхема?

+1

2 MHz при VCC 2V

20 MHz при VCC 4.5V

24 MHz при VCC 6V

20 MHz при VCC 4.5V

24 MHz при VCC 6V

+2

Там пара МК. Возможно, в постах это не упоминал, но проект немного разросся в ширь. Теперь мучаюсь с преобразователем PoE -> 5V. Скоро ожидается рабочий образец. В основном, проблема сейчас в этом.

На ПЛИС не получится (незнание языка) в основном. Но идея хороша.

Из минусов решения — дороговизна решения (замена Slave контроллера на ПЛИС — 50 рублей -> 500 рублей); большой корпус (беглый взгляд даёт самый просто вариант здесь, но тут УЖЕ «1270 LEs with 114 common I/O, 8K bits User Flash Memory») но не могу понять, мне этого хватило бы на создание 1кБ памяти, или нет… но вот НОГИ… =) Многовато, в общем.

Так что, по сути, тот проект не относится с работе с FPGA. Он будет полностью на микроконтроллерах и обвязке.

И, да, делать дисплеи на FPGA — это очень толсто =)

Про расширители Вам уже написали. У себя питаю от 5V и проблем с производительностью не замечал ни разу.

На ПЛИС не получится (незнание языка) в основном. Но идея хороша.

Из минусов решения — дороговизна решения (замена Slave контроллера на ПЛИС — 50 рублей -> 500 рублей); большой корпус (беглый взгляд даёт самый просто вариант здесь, но тут УЖЕ «1270 LEs with 114 common I/O, 8K bits User Flash Memory») но не могу понять, мне этого хватило бы на создание 1кБ памяти, или нет… но вот НОГИ… =) Многовато, в общем.

Так что, по сути, тот проект не относится с работе с FPGA. Он будет полностью на микроконтроллерах и обвязке.

И, да, делать дисплеи на FPGA — это очень толсто =)

Про расширители Вам уже написали. У себя питаю от 5V и проблем с производительностью не замечал ни разу.

0

Вот наша ошибка, как технарей, в том, что мы иногда пытаемся размышлять, как экономисты: 50 рублей, 500 рублей. И при общении с другом, у которого высшее образование в области финансов, есть свой бизнес (небольшое производство), я понимаю, что при разработке устройства, лично мне — разработчику не нужно думать про деньги, себестоимости и прочее, потому что в этом я вообще ничего не понимаю. Я начинаю рассуждать, мы это все анализируем и я понимаю, что это вообще детский лепет. Он вообще считает, что если я должен сделать устройство, то лучше, чтобы я его сделал быстро. Сколько оно будет стоить — уже его работа. А что внутри — это его совершенно не интересует: с задачей справляется, работает надежно — отлично!

Но если вот так задумываться, что есть 500 рублей? Допустим, это примерная стоимость часа работы сферического инженера в вакууме. То есть, если над кодом провозился день, то цена микросхемы в 50 или 500 рублей — уже нет никакой разницы. А если это микросхема STM стоимостью в 5 рублей за штуку? Но чтобы перетащить проект на нее требуется 1.5 месяца? Экономика! Но у меня совсем другое образование. Поэтому надо делать свою работу, пользуясь теми инструментами, что нам удобно. Если это AVR — да и отлично! Рука набита, вперед! Важен результат :)

Но если вот так задумываться, что есть 500 рублей? Допустим, это примерная стоимость часа работы сферического инженера в вакууме. То есть, если над кодом провозился день, то цена микросхемы в 50 или 500 рублей — уже нет никакой разницы. А если это микросхема STM стоимостью в 5 рублей за штуку? Но чтобы перетащить проект на нее требуется 1.5 месяца? Экономика! Но у меня совсем другое образование. Поэтому надо делать свою работу, пользуясь теми инструментами, что нам удобно. Если это AVR — да и отлично! Рука набита, вперед! Важен результат :)

0

И как это ни парадоксально, то же самое касается внутреннего перфекциониста разработчика, Если два устройства работают одинаково, но одно было разработано за неделю и код занял почти всю память, а второе за 1,5-2 месяца, но код в 10 раз меньше — какое выгоднее? Жестоко, но факт — первое. Ибо против математики не попрешь…

0

Дайте угадаю, статья из/для «Хакера»? :)

+1

Все-таки хотелось чуть больше объективности увидеть в статье. Мол вот плюсы, а вот здесь минусы.

ИМХО использовать ПЛИС стОит, когда стоит задача обработки цифрового сигнала и вот ну никак иначе. А когда начинается сложная логика или протокол связи, то все-равно внутрь ПЛИС приходится загружать какой-то из доступных микроконтроллеров (что приводит к еще большему веселью, и никак не отменяет нужды читать доки).

Ну и еще есть стандартные проблемы с восприятием подхода к… даже язык не поворачивается сказать «программированием ПЛИС». Это не программирование в привычном понимание. Программа — набор последовательных инструкций. В ПЛИС с непривычки очень здорово запутаться можно, а каждая ошибка превращается в 10 минут (почти что минимум) безделья и попивания чая на пересборку проекта.

Ну и чтобы еще больше «уравновесить» восторг статьи, чуть критики перечисленных плюсов:

1) не надо читать доки на МК. Зато придется читать доки на: USB, Ethernet, думать как перетащить известную написанную на С/С++ реализацию TCP/IP в ПЛИС, CAN и прочее-прочее добро. То, что есть готовые модули — это хорошо, но документацию то значит придется читать на них, не? а когда чужой модуль начинает вести себя… непредсказуемо? Да он же бесплатно был взят из инета! какие претензии?

2) ну про дедушку пример можно и про плис сказать. в сарайке есть плис, вот из него и соберем. А с тем, что есть эффективный по функциональности, цене в серии и, страшно сказать, времени на разработку МК под этот род задач, даже и разбираться не будем — лень же читать доки и все это в голове держать.

3 и 4ое — мне кажется когда в годах 70х придумывали языки программирование, то в каждой презентации были вот эти слова про «теперь можно сделать хорошо отлаженный модуль», «легко импортировать чужие модули».

ИМХО использовать ПЛИС стОит, когда стоит задача обработки цифрового сигнала и вот ну никак иначе. А когда начинается сложная логика или протокол связи, то все-равно внутрь ПЛИС приходится загружать какой-то из доступных микроконтроллеров (что приводит к еще большему веселью, и никак не отменяет нужды читать доки).

Ну и еще есть стандартные проблемы с восприятием подхода к… даже язык не поворачивается сказать «программированием ПЛИС». Это не программирование в привычном понимание. Программа — набор последовательных инструкций. В ПЛИС с непривычки очень здорово запутаться можно, а каждая ошибка превращается в 10 минут (почти что минимум) безделья и попивания чая на пересборку проекта.

Ну и чтобы еще больше «уравновесить» восторг статьи, чуть критики перечисленных плюсов:

1) не надо читать доки на МК. Зато придется читать доки на: USB, Ethernet, думать как перетащить известную написанную на С/С++ реализацию TCP/IP в ПЛИС, CAN и прочее-прочее добро. То, что есть готовые модули — это хорошо, но документацию то значит придется читать на них, не? а когда чужой модуль начинает вести себя… непредсказуемо? Да он же бесплатно был взят из инета! какие претензии?

2) ну про дедушку пример можно и про плис сказать. в сарайке есть плис, вот из него и соберем. А с тем, что есть эффективный по функциональности, цене в серии и, страшно сказать, времени на разработку МК под этот род задач, даже и разбираться не будем — лень же читать доки и все это в голове держать.

3 и 4ое — мне кажется когда в годах 70х придумывали языки программирование, то в каждой презентации были вот эти слова про «теперь можно сделать хорошо отлаженный модуль», «легко импортировать чужие модули».

+3

В ПЛИС с непривычки очень здорово запутаться можно, а каждая ошибка превращается в 10 минут (почти что минимум) безделья и попивания чая на пересборку проекта.

Используйте симуляцию (modelsim/questasim/бесплатные аналоги) ;)

Хотя, понимаю, что для маленьких проектов их может быть лениво писать)

+1

Каюсь, грешен. Основная цель статьи — привлечь людей к тому, чтобы они начали использовать ПЛИС. И я умышленно не стал говорить обо всех возможных проблемах на этом пути. Я не соврал, я просто не сказал всей правды :) К сожалению, секта ПЛИСоводов после этой строки лишится процента прихожан :(

Ну и считаю, что я обязан прокомментировать все тезисы, раз уж все так серьезно:

По поводу ПЛИС исключительно для ЦОС, тут не согласен. Плис ИМХО, постепенно вытеснит DSP, но я не профи в этой области. Просто мнение. Но считаю, что ПЛИС можно применять более широко, даже не создавая МК на кристалле.

В том и дело, что не всегда и не легко. Но тут надо решить для себя, над чем стоит ломать копья, а что не стоит твоего времени. Я не начну решать задачу на МК, допустим, КР1878ВЕ1, потому что у полученного опыта не будет будущего. Ну если только ради фана, спортивного интереса. В области МК я для себя решил, что если и буду тратить время на изучение нового МК, то это будет ARM. А в области схемотехники, обработки, генерации сигналов (ЦОС), в быстродействующих схемах — ПЛИС. Потому что эти знания пригодятся в будущем: процессоры ARM не перестанут производиться, а знания Verilog можно будет перетащить на другого производителя (Altera, Xilinx, Achronix, etc). Но я могу себе позволить ошибаться в выводах в области электроники, потому что она не является сферой моей профессиональной деятельности :)

Ну и считаю, что я обязан прокомментировать все тезисы, раз уж все так серьезно:

ИМХО использовать ПЛИС стОит, когда стоит задача обработки цифрового сигнала и вот ну никак иначе. А когда начинается сложная логика или протокол связи, то все-равно внутрь ПЛИС приходится загружать какой-то из доступных микроконтроллеров (что приводит к еще большему веселью, и никак не отменяет нужды читать доки).

По поводу ПЛИС исключительно для ЦОС, тут не согласен. Плис ИМХО, постепенно вытеснит DSP, но я не профи в этой области. Просто мнение. Но считаю, что ПЛИС можно применять более широко, даже не создавая МК на кристалле.

1) не надо читать доки на МК. Зато придется читать доки на: USB, EthernetВ случае применения МК, нужно читать доки и на МК и на USB, а если мк не справляется, то доки на другой_МК. А если они все не справляются — ставить еще один МК — они ж дешевые! В случае с ПЛИС нужно читать доки на USB и выбрать ПЛИС, в которую все влезет. Хотя бы чуть чуть, но меньше трудозатрат. Если МК будет внутри ПЛИС, то наверное будет то же самое, не пробовал. Но количество разных технологий в проекте уменьшится. Повторюсь, я не профессионал в этой области, они сейчас делают все системы на одном кристалле. Видимо, в этом есть какой-то смысл. А документацию читать все равно придется — тут согласен (блин, еще народ ушел).

2) ну про дедушку пример можно и про плис сказать.Вот! В точку. Это известная проблема, когда человек становится увлечен какой-то технологией: он начинает ее пихать вообще везде. Питонисты пишут все на питоне, даже написали свой HDL — MyHDL. Любители Erlang начинают писать интерфейсы с пользователем (я не имею в виду N2O) и бухгалтерские системы. Любители МК делают регуляторы уровня воды в баке, хотя все чудно можно разрулить на реле… И список можно продолжать. Давайте добавим ПЛИС в арсенал, но не будет пихать везде.

3 и 4ое — мне кажется когда в годах 70х придумывали языки программирование, то в каждой презентации были вот эти слова про «теперь можно сделать хорошо отлаженный модуль», «легко импортировать чужие модули».

В том и дело, что не всегда и не легко. Но тут надо решить для себя, над чем стоит ломать копья, а что не стоит твоего времени. Я не начну решать задачу на МК, допустим, КР1878ВЕ1, потому что у полученного опыта не будет будущего. Ну если только ради фана, спортивного интереса. В области МК я для себя решил, что если и буду тратить время на изучение нового МК, то это будет ARM. А в области схемотехники, обработки, генерации сигналов (ЦОС), в быстродействующих схемах — ПЛИС. Потому что эти знания пригодятся в будущем: процессоры ARM не перестанут производиться, а знания Verilog можно будет перетащить на другого производителя (Altera, Xilinx, Achronix, etc). Но я могу себе позволить ошибаться в выводах в области электроники, потому что она не является сферой моей профессиональной деятельности :)

0

Основная цель статьи — привлечь людей к тому, чтобы они начали использовать ПЛИС.

Люди должны начать использовать ПЛИС только тогда, когда это экономически выгодно и действительно необходимо)

К примеру:

Есть ТЗ на какой-то девайс, и если готовый MCU/CPU не может удовлетворить эти требования ( по производительности, к примеру ), то разработчик ищет варианты, как это можно реализовать. И FPGA является одним из таких вариантов. Для высокопроизводительных вычислений в этом вопросе рядом встает и GPU. А может проще купить мощнее сервер или обсчитывать всё на кластере из серверов?

ЦОС, к примеру, может обсчитываться на специальных готовых DSP-чипах. Для каких-то задач будет проще взять такой процессор, чем писать это всё на FPGA.

+1

А если мне просто интересно? )

В моем случае шаг в сторону ПЛИС произошел после тщетных попыток сделать клон электрооргана Юность-70 на базе AVR. Мы очень долго обсуждали эту тему на форуме, я ставил эксперименты с делителями на AVR и больше 10 меандров сделать не мог. А нужно было их по 12 на октаву, да еще и менять громкость регистров, сделать частотную модуляцию, вырисовывалась архитектура из 10 AVRок, либо с ограниченным количеством голосов, либо цифровое решение с ЦАП. Четырехголосный электроорган никому не надо. Цифровой орган у всех и так есть. Аналоговая тема в звуке — вообще отдельный разговор. Но суть в том, что надо отдельно больше 100 меандров, в оригинале это делители на счетчиках. Поэтому надо либо делать то же самое на десяти корпусах, либо какие-то современные решения. О чем я мог подумать, кроме ПЛИС?

В моем случае шаг в сторону ПЛИС произошел после тщетных попыток сделать клон электрооргана Юность-70 на базе AVR. Мы очень долго обсуждали эту тему на форуме, я ставил эксперименты с делителями на AVR и больше 10 меандров сделать не мог. А нужно было их по 12 на октаву, да еще и менять громкость регистров, сделать частотную модуляцию, вырисовывалась архитектура из 10 AVRок, либо с ограниченным количеством голосов, либо цифровое решение с ЦАП. Четырехголосный электроорган никому не надо. Цифровой орган у всех и так есть. Аналоговая тема в звуке — вообще отдельный разговор. Но суть в том, что надо отдельно больше 100 меандров, в оригинале это делители на счетчиках. Поэтому надо либо делать то же самое на десяти корпусах, либо какие-то современные решения. О чем я мог подумать, кроме ПЛИС?

+1

:)

Решение на 10 AVR не понравилось -> нашли альтернативу в виде FPGA. Это как раз то, о чем я говорю — надо использовать FPGA только тогда, когда надо, т.к. это не серебряная пуля. Если в другом проекте и без FPGA обходятся, то не надо делать что-то на FPGA)

С другой стороны, в масс-продакте цена может сильно влиять на вариант реализации. И если вариант на FPGA не вписывается в бюджет, то…

Во-вторых, хороших FPGA программистов для больших проектов сейчас сложно найти.

Решение на 10 AVR не понравилось -> нашли альтернативу в виде FPGA. Это как раз то, о чем я говорю — надо использовать FPGA только тогда, когда надо, т.к. это не серебряная пуля. Если в другом проекте и без FPGA обходятся, то не надо делать что-то на FPGA)

С другой стороны, в масс-продакте цена может сильно влиять на вариант реализации. И если вариант на FPGA не вписывается в бюджет, то…

Во-вторых, хороших FPGA программистов для больших проектов сейчас сложно найти.

+1

Все равно не пойму этой ненависти к ПЛИС. Задача получить 100 меандров по отдельности, путем деления частоты основного генератора. Чем я должен мотивироваться в сторону 10 AVR'ов и не принять решение на 1-й CPLD + 1AVR?

+1

Где ненависть к ПЛИС?)

Я их очень люблю, см. мой профиль)

Просто Вы заявляете, что надо использовать FPGA. На кого направлена статья? На людей, которые не определились — нужна им FPGA или нет для своих задач. Допустим, прочитали на википедии для чего могут они использовать. Не думаю, что после Вашей статьи им еще стало всё понятнее и они больше замотивированы, что FPGA им поможет для решения своих задач.

Ваш пример с Юностью намного более показателен, чем то, что написано в статье. Вы решили конкретную задачу на FPGA и если у человека, который не определился нужно ему это или нет, возникает подобная задача — он поймет, что FPGA это именно то, что ему надо.

Я их очень люблю, см. мой профиль)

Просто Вы заявляете, что надо использовать FPGA. На кого направлена статья? На людей, которые не определились — нужна им FPGA или нет для своих задач. Допустим, прочитали на википедии для чего могут они использовать. Не думаю, что после Вашей статьи им еще стало всё понятнее и они больше замотивированы, что FPGA им поможет для решения своих задач.

Ваш пример с Юностью намного более показателен, чем то, что написано в статье. Вы решили конкретную задачу на FPGA и если у человека, который не определился нужно ему это или нет, возникает подобная задача — он поймет, что FPGA это именно то, что ему надо.

+1

На кого направлена статья?

На людей, которые пока не решились начать, потому что у них недостаточно информации. Вот пример статья, там об этом подробнее написано. У людей есть желание начать применять ПЛИС — это цель, но не знаем количество шагов до цели и время в пути. Непонятно какую фирму взять, какой язык, какую борду, где купить, куча вопросов. Я пытаюсь снять хотя бы часть этой неопределенности.

Вот даже пример ниже от Олега Анатольевича:

Чувствую что во многих проектах применение простеньких и недорогих ПЛИС мне могло бы пригодиться но никак не соберусь начать их освоение.

Ну и вы, как профессионал, скажите, может я действительно зря людей мотивирую? В заблуждение ввожу? А статью убрать надо…

0

Если Вы ставите людей замотивировать что-то сделать (а это похвально и в этом плане я Вас полностью поддерживаю), то сделайте статью с нуля, начиная что и как надо поставить, выбором девкита, описать все шаги, и получить реальный осязаемый продукт. Выложите проект с исходниками, покажите, что сделать обработку ЦОС на FPGA реально просто. Человек просто возмет, купит плату, аналогичную той, что вы используете, по шагам пройдется и получит аналогичный результат.

Мой коллега делал подобную статью: habrahabr.ru/post/235707/. Там расписаны все шаги, и любой просто повторит их и получит такой же результат, что и в статье. Что я должен повторить в вашей статье и какой результат получить?

Так же надо показать альтернативу, что реализация на MCU/CPU займет больше времени/будет не выгодной/не производительной и так далее. К примеру, вы выбрали Altera и Verilog без какой-то ощутимой мотивации. И даже холивар VHDL vs Verilog не развели)

Мой коллега делал подобную статью: habrahabr.ru/post/235707/. Там расписаны все шаги, и любой просто повторит их и получит такой же результат, что и в статье. Что я должен повторить в вашей статье и какой результат получить?

Так же надо показать альтернативу, что реализация на MCU/CPU займет больше времени/будет не выгодной/не производительной и так далее. К примеру, вы выбрали Altera и Verilog без какой-то ощутимой мотивации. И даже холивар VHDL vs Verilog не развели)

+1

Да, есть о чем подумать. Сделаю выводы :)

Я обычно свое мнение при себе держу, но в целях повышения качества… Статья подробная, исчерпывающая, согласен. Но, меня, почему-то не заинтересовала и ни к чему не смотивировала. Почему, с ходу не смогу сказать, тут надо как-то аналитически рассмотреть этот вопрос. Прочитал, как константу, факт и все. Единственное, что меня заинтересовало: стоимость платы. Моя статья наоборот — пустая, никакой конкретики. Степень влияния на аудиторию оценить сложно, можно только плюсики и просмотры сравнить, но показатель ли это!? Очевидно, что статьи нужно делать и не просто исчерпывающие, и не зрелищные, но пустые. Будем работать над этим )

По поводу Altera, работаю не один, совместно так решили — без особых обоснований. Как и Verilog — из за похожести на си (как обычно пишут). Но не более того. Я начинал с нуля, поэтому особой разницы то не было. Но тема холиварная, поэтому я эти пункты «проехал» быстро и без шума.

Я обычно свое мнение при себе держу, но в целях повышения качества… Статья подробная, исчерпывающая, согласен. Но, меня, почему-то не заинтересовала и ни к чему не смотивировала. Почему, с ходу не смогу сказать, тут надо как-то аналитически рассмотреть этот вопрос. Прочитал, как константу, факт и все. Единственное, что меня заинтересовало: стоимость платы. Моя статья наоборот — пустая, никакой конкретики. Степень влияния на аудиторию оценить сложно, можно только плюсики и просмотры сравнить, но показатель ли это!? Очевидно, что статьи нужно делать и не просто исчерпывающие, и не зрелищные, но пустые. Будем работать над этим )

По поводу Altera, работаю не один, совместно так решили — без особых обоснований. Как и Verilog — из за похожести на си (как обычно пишут). Но не более того. Я начинал с нуля, поэтому особой разницы то не было. Но тема холиварная, поэтому я эти пункты «проехал» быстро и без шума.

0

О мотивации всё Джордж Карлин в своё время сказал)

Мне, например, интересен SystemC, что бы понять я могу использовать в своей разработке или нет. Статья «Сделай шаг к SystemC» где будет лейтмотивом, что «SystemC это круто», не особо поможет мне разобраться в теме.

А статья «Сравниваем SystemVerilog и SystemC», где разработчик делает НЕ счетчик, а что-то более менее серьезное на обоих языка с пошаговыми инструкциями и сравнениями по частоте, логическим элементам, удобству и гибкости намного больше даст пищи для размышлений.

Мне, например, интересен SystemC, что бы понять я могу использовать в своей разработке или нет. Статья «Сделай шаг к SystemC» где будет лейтмотивом, что «SystemC это круто», не особо поможет мне разобраться в теме.

А статья «Сравниваем SystemVerilog и SystemC», где разработчик делает НЕ счетчик, а что-то более менее серьезное на обоих языка с пошаговыми инструкциями и сравнениями по частоте, логическим элементам, удобству и гибкости намного больше даст пищи для размышлений.

0

Как по мне, так под контроллеры сложнее программировать.

У hdl более предсказуемое поведение.

И там тоже непонятно какую фирму взять, asm или Cи…

У hdl более предсказуемое поведение.

И там тоже непонятно какую фирму взять, asm или Cи…

+1

Когда до этого много писал на обычных языках программирования, то понять почему оно работает не так в hdl сложновато. Привыкнуть к тому что цикл будет развернут во время компиляции, и прочие хитрости не легко. Поэтому и кажется что это сложней.

0

Вот что меня действительно отпугивало (да и продолжает отпугивать) в ПЛИС — так это тот факт, что даже на начальном уровне (см. фотографии в статье) я вижу ужасный TQFP80, а то и 100 и более, практически гарантирующий мне тот факт, что моя разработка не выйдет из состояния «поделки» на development board даже теоретически. Работа с МК не является тем, чем я зарабатываю на жизнь, у меня нет бригады монтажников или парка монтажных автоматов, которые приделают этого монстра на мою плату за секунду, а потому все довольно печально. К сожалению.

И я с радостью попробую, если шаг ног у чипов будет хотя бы 0,8мм.

И я с радостью попробую, если шаг ног у чипов будет хотя бы 0,8мм.

0

У многих современных ПЛИС шаг 0.8, хотя полно и старых BGA с шагом 1 мм.

0

Приделать монстра на плату не проблема, абы плата уже была готовая… припаять можно обычным паяльником с жалом типа «волна» или использовать специальную паяльную пасту с шариками припоя и паяльным феном.

0

Если смотреть на начальные CPLD www.chipfind.ru/catalog/ic/cplds/?&field=price&order=asc то там вполне есть корпуса типа 44-PLCC конечно ресурсов в ней не так много, но для начала зачастую хватает.

0

CPLD с 10 макроячейками есть, судя по этой таблице, даже в SOIC-24…

теперь осталось выяснить, сколько их для чего (примерно) нужно

было бы, кстати, интересно почитать

теперь осталось выяснить, сколько их для чего (примерно) нужно

было бы, кстати, интересно почитать

0

Да, пожалуй, стоит в квартусе поэкспериментировать на этот счет.

0

Вот сейчас навскидку взял первый попавшийся на Ебее CPLD от Altera.

EPM7032SLC44-10 IC MAX 7000 CPLD 32 44-PLCC — 135.23 рубля с доставкой.

Параметры: Usable gates 600, Macrocells 32, fCNT 151.5 MHz

8 битный счетчик (вход clk и 8 линий выхода) — занял 8 из 32х

16-битный счетчик (вход clk и 8 линий выхода) — занял 16 из 32х

Дешифратор-преобразователь в семисегментный код — 8 из 32х

Эммм, ну не знаю. Преобразователь STEP-DIR для платы шагового движка — 10 из 32х

Приемник SPI занял 14 из 32х. И если принятый байт принимать в качестве параметра, для ШИМ, то получается тик в тик 32 из 32х!

Логика на verilog, описывающая работу спектрумовской ay-8910 не влезло в самый большой MAX из линейки, заняв 263 из 256 возможных ячеек.

Примерно такой расклад.

EPM7032SLC44-10 IC MAX 7000 CPLD 32 44-PLCC — 135.23 рубля с доставкой.

Параметры: Usable gates 600, Macrocells 32, fCNT 151.5 MHz

8 битный счетчик (вход clk и 8 линий выхода) — занял 8 из 32х

Verilog counter

module test01(clk, out);

input wire clk;

output reg [7:0] out;

initial begin

out = 0;

end

always @(posedge clk) begin

out <= out + 1;

end

endmodule

16-битный счетчик (вход clk и 8 линий выхода) — занял 16 из 32х

Дешифратор-преобразователь в семисегментный код — 8 из 32х

Verilog 7seg

module test01(data, SEG);

input wire[3:0] data;

output wire[7:0] SEG;

reg [6:0] SEG_buf;

always @ (data)

begin

case(data)

4'h0: SEG_buf <= 7'b0111111;

4'h1: SEG_buf <= 7'b0000110;

4'h2: SEG_buf <= 7'b1011011;

4'h3: SEG_buf <= 7'b1001111;

4'h4: SEG_buf <= 7'b1100110;

4'h5: SEG_buf <= 7'b1101101;

4'h6: SEG_buf <= 7'b1111101;

4'h7: SEG_buf <= 7'b0000111;

4'h8: SEG_buf <= 7'b1111111;

4'h9: SEG_buf <= 7'b1101111;

4'hA: SEG_buf <= 7'b1110111;

4'hB: SEG_buf <= 7'b1111100;

4'hC: SEG_buf <= 7'b0111001;

4'hD: SEG_buf <= 7'b1011110;

4'hE: SEG_buf <= 7'b1111001;

4'hF: SEG_buf <= 7'b1110001;

default: SEG_buf <= 7'b0111111;

endcase

end

assign SEG = {1'b0,SEG_buf};

endmodule

Эммм, ну не знаю. Преобразователь STEP-DIR для платы шагового движка — 10 из 32х

Verilog stepdir

module stepdir(input STEP, input DIR,output reg [3:0] OUT);

reg [3:0] state;

initial

begin

state=0;

end

always@(posedge STEP)begin

if (DIR==1) begin

state=state+1'b1;

end else if (DIR==0) begin

state=state-1'b1;

end

case (state)

0: OUT=4'b1000;

1: OUT=4'b1100;

2: OUT=4'b0100;

3: OUT=4'b0110;

4: OUT=4'b0010;

5: OUT=4'b0011;

6: OUT=4'b0001;

7: OUT=4'b1001;

endcase

end

endmoduleПриемник SPI занял 14 из 32х. И если принятый байт принимать в качестве параметра, для ШИМ, то получается тик в тик 32 из 32х!

Verilog SPIPWM

module test01(clk, SCK, MOSI, MISO, SSEL, LED, PWM_out);

input clk;

input SCK, SSEL, MOSI;

output MISO;

output LED;

output PWM_out;

// sync SCK to the FPGA clock using a 3-bits shift register

reg [2:0] SCKr; always @(posedge clk) SCKr <= {SCKr[1:0], SCK};

wire SCK_risingedge = (SCKr[2:1]==2'b01); // now we can detect SCK rising edges

wire SCK_fallingedge = (SCKr[2:1]==2'b10); // and falling edges

// same thing for SSEL

reg [2:0] SSELr; always @(posedge clk) SSELr <= {SSELr[1:0], SSEL};

wire SSEL_active = ~SSELr[1]; // SSEL is active low

wire SSEL_startmessage = (SSELr[2:1]==2'b10); // message starts at falling edge

wire SSEL_endmessage = (SSELr[2:1]==2'b01); // message stops at rising edge

// and for MOSI

reg [1:0] MOSIr; always @(posedge clk) MOSIr <= {MOSIr[0], MOSI};

wire MOSI_data = MOSIr[1];

// we handle SPI in 8-bits format, so we need a 3 bits counter to count the bits as they come in

reg [2:0] bitcnt;

reg byte_received; // high when a byte has been received

reg [7:0] byte_data_received;

reg [7:0] pwm_counter;

initial

pwm_counter = 0;

always @(posedge clk)

pwm_counter <= pwm_counter + 1;

assign PWM_out = (byte_data_received>pwm_counter); // comparator

always @(posedge clk)

begin

if(~SSEL_active)

bitcnt <= 3'b000;

else

if(SCK_risingedge)

begin

bitcnt <= bitcnt + 3'b001;

// implement a shift-left register (since we receive the data MSB first)

byte_data_received <= {byte_data_received[6:0], MOSI_data};

end

end

always @(posedge clk) byte_received <= SSEL_active && SCK_risingedge && (bitcnt==3'b111);

// we use the LSB of the data received to control an LED

reg LED;

always @(posedge clk) if(byte_received) LED <= byte_data_received[0];

endmoduleЛогика на verilog, описывающая работу спектрумовской ay-8910 не влезло в самый большой MAX из линейки, заняв 263 из 256 возможных ячеек.

Примерно такой расклад.

+1

Конечно, есть случаи, когда плату под ПЛИС нужно разрабатывать самому. Я себя успокаиваю тем, что мне будет достаточно существующих плат, а все остальное к ним делать внешними модулями. Удобно: борда кончилась — взял другую, перекинул на другие ножки и вперед.

А вот, к примеру, Олег Анатольевич progchip666 вообще считает:

А вот, к примеру, Олег Анатольевич progchip666 вообще считает:

В последнее время появилось огромное количество готовых решений — демонстрационных плат и различных универсальных программируемых модулей по доступным ценам. Собрать из них готовое решение уникальной задачи часто проще и дешевле, чем разработка специального прибора. Разработка собственно электроники сводится к созданию конструктива, да простеньких объединительных и согласующих плат.

0

Спасибо за упоминание. Тема статьи очень интересная, но статья написана в Западном стиле. Цель не столько объяснить что и как делать, сколько замотивировать. Возможно это и правильно. Сам нахожусь в такой же ситуации. Хорошо разбираюсь в схемотехнике. Чувствую что во многих проектах применение простеньких и недорогих ПЛИС мне могло бы пригодиться но никак не соберусь начать их освоение.

Помнится то же самое было с DDS. Синтезаторы казались мне чем то сверхъестественным, а на деле оказалось всё очень просто.

Помнится то же самое было с DDS. Синтезаторы казались мне чем то сверхъестественным, а на деле оказалось всё очень просто.

+1

Возможно, если Вы укажете еще парочку хабов, то статью прочитает больше народа. Например, хаб DIY подошел бы…

+1

Парочка вопросов возникла:

Вопрос первый. Рекомендация ставить Quartus II V11 чем обоснована? На сайте производителя говорится о последнем релизе аж V14.

Второй вопрос: Где граница бесплатных сред разработки? На сайте в разделе «Buy» стоят ужасные 4-значные долларовые суммы, в то время как V11-V12 декларированы как «free».

Вопрос первый. Рекомендация ставить Quartus II V11 чем обоснована? На сайте производителя говорится о последнем релизе аж V14.

Второй вопрос: Где граница бесплатных сред разработки? На сайте в разделе «Buy» стоят ужасные 4-значные долларовые суммы, в то время как V11-V12 декларированы как «free».

0

В 14 версии убрали поддержку Cyclone I-III, насколько я помню. Так же 14 версия вроде только 64-битная.

У Quartus есть Web Edition — бесплатная версия. Сравнение можно найти здесь: www.altera.com/literature/po/ss_quartussevswe.pdf

Для маленьких FPGA и маленьких проектов легко подходят старые версия квартуса (9-11), они и меньше весят)

У Quartus есть Web Edition — бесплатная версия. Сравнение можно найти здесь: www.altera.com/literature/po/ss_quartussevswe.pdf

Для маленьких FPGA и маленьких проектов легко подходят старые версия квартуса (9-11), они и меньше весят)

+1

На мой взгляд, самая лучшая версия Квартуса — это 9.1. Во-первых, там есть режим совместимости со старым добрым Max Plus II, она поддерживает, по-моему, максимальное число камней, от древних ПиЭльДэшек типа MAX3000 до мощных каменюг типа Стратикс 4 и Циклон 5 (хоть и прелиминари, но я проекты успешно собирал) и, главное, это — последняя версия, в который был собственный весьма простой и удобный симулятор, а не это убожество под названием «Моделсим».

0

У Моделсима немного другое назначение, чем простой симулятор)

Большие проекты без Моделсима или аналогичного симулятора невозможно быстро разрабатывать.

Большие проекты без Моделсима или аналогичного симулятора невозможно быстро разрабатывать.

+2

Я сейчас Icarus Verilog для себя открыл. Очень удобно.

0

Конечно не моего ума дело, но я бы запретил на «Хабре» статьи подобного рода. Во-первых статей для начинающих плисоводов в И-нете на всех возможных языках (включая, разумеется, русский) пруд пруди. А главное — авторы подобных статей не понимают одного: программирование FPGA нельзя «попробовать»! Это можно попробовать «попрограммировать» на компе или игрушечную платку с «восьмирёночком» типа «Ардуино». А вот с ПЛИС — это как изучать иностранный язык или играть на музыкальном инструменте, либо ты этим занимаешься по-серъёзному и регулярно, либо не нужно тратить на это время вообще. Кроме того, нужен совсем другой объём знаний по сравнению с программированием. По-крайней мере, истинный плисовод должен очень хорошо разбираться в электронике, как показывает моя многолетняя практика вменяемого плисовода можно сделать только из грамотного электронщика.

+1

Ну вот я в своё время именно пробовал. Просто для интереса. Хотя потом несколько раз меня капитально выручала моя DEV плата когда нужно было прошить всякие многоногие FLASH чипы а программатора нужного не было. В общем-то всё решает массовость когда то и программирование микроконтроллеров было уделом избранных. Сейчас этим занимаются все кому лень. FPGA конечно в разы сложней(с одной стороны), однако чем больше будет доступной информации тем проще будет попробовать. А вот то что ПЛИСовод должен разбираться в электронике с этим полностью согласен, и я в моём случае как раз попытка разобраться в ПЛИС заставила разбираться в электронике.

+1

Оно и понятно, потому что ПЛИС — это конфигурируемая электрическая схема а не микроконтроллер.

Надо просто принять что программы для ПЛИС — это набор функций связанных или не связанных друг с другом и внешними выводами. Никаких «последовательных» шагов выполнения в таких программах нет — все функции выполняются непрерывно и параллельно.

Надо просто принять что программы для ПЛИС — это набор функций связанных или не связанных друг с другом и внешними выводами. Никаких «последовательных» шагов выполнения в таких программах нет — все функции выполняются непрерывно и параллельно.

+2

Я бы сказал, что программы для ПЛИС — это чистая схемотехника, и ничего общего с программированием микроконтроллеров. Т.е. писать программу на verilog, всё равно что рисовать принципиальную (функциональную) схему. Как у художников, которые вроде рисуют, а говорят, что пишут картины. Просто надо это почувствовать, и твои картины(программы) будут отличаться от детсадовского рисунка. Как-то так.

+1

Вроде бы и согласен с тем, что плисоводство занятие очень время- внимание- трудоёмкое, но запрещать не надо.

Автор неделю знакомился с ПЛИС, затем за двадцать минут сделал звук — надцать меандров. Даёт ли это право писать кипятком, постить непристойные картинки и зазывать за собой? Почему нет, он решил свою задачу — создал основу для синтезатора.

И хочу подчеркнуть, что появление прикладных проектов на ПЛИС тормозит не столько концептуальная сложность, сколько бедность инструментария, так что про Quartus 9 я с вами согласен, было неприятно, я правда перешёл на новые версии и стал отлаживаться через VGA.

Автор неделю знакомился с ПЛИС, затем за двадцать минут сделал звук — надцать меандров. Даёт ли это право писать кипятком, постить непристойные картинки и зазывать за собой? Почему нет, он решил свою задачу — создал основу для синтезатора.

И хочу подчеркнуть, что появление прикладных проектов на ПЛИС тормозит не столько концептуальная сложность, сколько бедность инструментария, так что про Quartus 9 я с вами согласен, было неприятно, я правда перешёл на новые версии и стал отлаживаться через VGA.

0

Если не секрет, что Вы вкладываете в «бедность инструментария»?

+1

1. Языки HDL. Созданы скорее для верификации чем для синтеза, низкоуровневы, слабые средства обобщённого программирования, описание функционала распадается на синхронную и асинхронную части.

2. Утилиты и среды. Громоздки, неинтуитивны, часто непонятно, как сделать простую вещь. Например, отладили вы прошивку и хотите залить её в ППЗУ. Чего ожидаешь — поставить в загрузчике галку — прошить в ППЗУ. А на деле надо сначала отдельно копать настройки проекта, сгенерировать специальный файл, затем хитро настраивать загрузчик, потом переключить плату в специальный режим, прошить, переключить обратно. В лучшем случае, производитель платы всё это по шагам расписал, но надо ещё сообразить где искать. kluwert упомянул ситуацию, когда из Qwartus-а выкинули привычное средство отладки.

2. Утилиты и среды. Громоздки, неинтуитивны, часто непонятно, как сделать простую вещь. Например, отладили вы прошивку и хотите залить её в ППЗУ. Чего ожидаешь — поставить в загрузчике галку — прошить в ППЗУ. А на деле надо сначала отдельно копать настройки проекта, сгенерировать специальный файл, затем хитро настраивать загрузчик, потом переключить плату в специальный режим, прошить, переключить обратно. В лучшем случае, производитель платы всё это по шагам расписал, но надо ещё сообразить где искать. kluwert упомянул ситуацию, когда из Qwartus-а выкинули привычное средство отладки.

0

1. Если под «низким уровнем» языка подразумевается то, что надо описывать каждый такт/регистр, то существует класс задач, где без этого не обойтись, что бы выжать нужную производительность. Процессор Opensparc, к примеру, написан на verilog'e и от этого («низкий уровень»)вряд ли можно будет уйти в ближайшее время.

Если хочется писать на С, но на FPGA, то для определенных задач можно попробовать использовать OpenCL, но сколько за Вас квартус производительность выжмет, столько и будет.

2. Не могу согласиться. Да, у Квартуса бывают вещи не самые интуитивные, но всё приходит с опытом :) Пример, что Вы привели, где неясно что прошивать — это нюансы конкретной борды.

Если хочется писать на С, но на FPGA, то для определенных задач можно попробовать использовать OpenCL, но сколько за Вас квартус производительность выжмет, столько и будет.

2. Не могу согласиться. Да, у Квартуса бывают вещи не самые интуитивные, но всё приходит с опытом :) Пример, что Вы привели, где неясно что прошивать — это нюансы конкретной борды.

+1

«существует класс задач» — не аргумент. Существует класс задач, которые программируют только на ассемблере.

Правда, не очень очевидно, как повышать уровень. Чего хотелось бы иметь: пусть надо потоком вычислять sin(x) + x*y + 100*x в конвейере; У меня есть модули для синуса и умножения, но каждый работает своё число тактов. Сейчас мне придётся самому их синхронизовать, а я хочу чтобы это делалось автоматически.

Куча ошибок возникает из-за преобразования разрядностей, особенно, когда работаешь со знаковыми числами. При этом выдаются такие кучи предупреждений из которых 90% совсем не по делу, что читать их невозможно. Можно от всех ворнингов избавиться, явно записав все преобразования, но при этом текст совершенно теряет читабельность.

Правда, не очень очевидно, как повышать уровень. Чего хотелось бы иметь: пусть надо потоком вычислять sin(x) + x*y + 100*x в конвейере; У меня есть модули для синуса и умножения, но каждый работает своё число тактов. Сейчас мне придётся самому их синхронизовать, а я хочу чтобы это делалось автоматически.

Куча ошибок возникает из-за преобразования разрядностей, особенно, когда работаешь со знаковыми числами. При этом выдаются такие кучи предупреждений из которых 90% совсем не по делу, что читать их невозможно. Можно от всех ворнингов избавиться, явно записав все преобразования, но при этом текст совершенно теряет читабельность.

0

По-крайней мере, истинный плисовод должен очень хорошо разбираться в электронике, как показывает моя многолетняя практика вменяемого плисовода можно сделать только из грамотного электронщика.

Соглашусь лишь отчасти. Для разработок всё сам нужно ковать плисовода из электронщика. Для командной работы в больших проектах иногда полезнее грамотно составить ТЗ программисту с учетом схемных ограничений. И получить от него более быстрый результат и удобный на Verilog проект. Который гораздо лучше ложится потом в ПЛИС. В комментариях есть мнение, что программа на ПЛИС это перписывание схемы на Verilog. Если отойти от этой практики, то схемы получаются гораздо лучше. Иногда пытаясь описать «как в схеме» получается каша, хотя этот кусок можно было описать в двух блоках. Я сам себя иногда на этом ловлю. И в проектах коллег вижу, перписывание некоторых таких частей дает иногда заметный прирост в скорости.

+1

Хотелось бы где-нибудь почитать, наверняка сложилась практика по и конкретные приемы, которые приводят к сокращению количества использованной логики. Потому что пробовал переписывать код и глядеть результат по ресурсам. Почти всегда получается переписать логику так, чтобы она синтезировалась более экономно. Обычно к этому приходит упрощение, сокращение логики, описание условий через else if или case.

Так что если есть что — подскажите!

Так что если есть что — подскажите!

0

Для Альтеры см. «Recommended HDL Coding Styles»: www.altera.com/literature/hb/qts/qts_qii51007.pdf

Какие-то общие вещи см. Steve Kilts «Advanced FPGA Design».

Какие-то общие вещи см. Steve Kilts «Advanced FPGA Design».

+2

Я не имел ввиду экономию ресурсов -10 или -20 LE.

Я имел ввиду, что в основном в итоге мы получаем прирост в скорости. И иногда в LE, за счёт регистров.

У меня был пробный проект с LVDS, на плате не предназначенной для передачи дифференциальных сигналов. При максимальных 622 МБит/с я смог получить 590 МБит/с. По витой паре из МГТФ, между двумя платами, с кривой синхронизацией. Нужно было проверить идею отказа от параллельной шины и замены её на последовательные, без использования гигабитных интерфейсов.

Еще было задание выжать максимум из старой платы, на которой не получалось сделать положенные 100 блоков работающие на 5 МГц. В итоге влезли все 100 и проект занимает менее 95% ресурсов.

Если электронщик думает о том как он бы сделал проект на рассыпухе, то он получит кучу неприятностей в виде неуспевающей логики. Если пытаться завернуть всё в примитивы триггеров и ячеек, то это будет долго и не всегда эффективно. Что-то оптимизирует компилятор, что-то не сможет. Электронщик будет рассказывать компилятору КАК делать, а программист (FPGA-designer) — ЧТО делать. И если у меня проект где-то не влазит, то значит я сильно затягиваю в сторону КАК.

Я слушал курсы по Xilinx и VHDL. Работаю с Altera и на Verilog.

Я начинал с «Introduction to VHDL». Потом был курс «Design for perfomance». Оба от Xilinx. Были еще курсы по моделированию и SystemVerilog. Но в последнем я тогда ни чего не понял, так как работал с схемами и платами.

Я имел ввиду, что в основном в итоге мы получаем прирост в скорости. И иногда в LE, за счёт регистров.

У меня был пробный проект с LVDS, на плате не предназначенной для передачи дифференциальных сигналов. При максимальных 622 МБит/с я смог получить 590 МБит/с. По витой паре из МГТФ, между двумя платами, с кривой синхронизацией. Нужно было проверить идею отказа от параллельной шины и замены её на последовательные, без использования гигабитных интерфейсов.

Еще было задание выжать максимум из старой платы, на которой не получалось сделать положенные 100 блоков работающие на 5 МГц. В итоге влезли все 100 и проект занимает менее 95% ресурсов.

Если электронщик думает о том как он бы сделал проект на рассыпухе, то он получит кучу неприятностей в виде неуспевающей логики. Если пытаться завернуть всё в примитивы триггеров и ячеек, то это будет долго и не всегда эффективно. Что-то оптимизирует компилятор, что-то не сможет. Электронщик будет рассказывать компилятору КАК делать, а программист (FPGA-designer) — ЧТО делать. И если у меня проект где-то не влазит, то значит я сильно затягиваю в сторону КАК.

Я слушал курсы по Xilinx и VHDL. Работаю с Altera и на Verilog.

Я начинал с «Introduction to VHDL». Потом был курс «Design for perfomance». Оба от Xilinx. Были еще курсы по моделированию и SystemVerilog. Но в последнем я тогда ни чего не понял, так как работал с схемами и платами.

+1

Программист может не доехать, что такое критический путь и как его разорвать. Опять же программист может и не увидеть проблемы схем с несколькими синхронизациями. Вообщем и целом просто программиста, не знающего схемотехнику сложно обучить писать на HDL, чистый схемотехник, который круто работает на рассыпухе, но не знает программирования тоже не очень подходит. Нужен специалист на стыке. Если вы хотите юзать программиста, то стоит использовать OpenCL, как мне кажется.

+2

Согласен. Но одно дело научить программиста этим вещам, и совсем другое ПЕРЕучить электронщика.

0

Одинаково, нюансов и там и там достаточно, тем более, что программист не сможет пользоваться конструкциями ООП. Банально ни какие супер-пупер парадигмы программирования при написании на Verilog'e не нужны… Нужен программист системщик, который хорошо кодит на чистом Си. А вот если человек писал на C# он будет постоянно неприятно удивляться. ООП есть только в SystemVerilog и только для верификации.

0

Опять же любой программист мыслит последовательно, кроме работающих в области параллельных вычислений, для разработки на HDL языках все действия чаще всего выполняются параллельно, и мыслить нужно параллельно и в тактах вашего устройства… Программист точно не каждый это сможет понять.

0

Берем Verilog — потомучто…

Очень странная рекомендация использовать Verilog для ПЛИС Altera. Универсальность ради универсальности? Чем родной AHDL плох?

0

Думаю, AHDL менее популярен, чем VHDL/Verilog. На оpencores большинство проектов на VHDL/Verilog.

Попробуйте в МegaWizard сгенерить DDR, PCIe или Ethernet контроллер на AHDL) Как думаете, почему Альтера не дает это сделать?

Попробуйте в МegaWizard сгенерить DDR, PCIe или Ethernet контроллер на AHDL) Как думаете, почему Альтера не дает это сделать?

+2

Потому, что сама их продает.

0

В смысле продает?

DDR и PCIe контроллеры бесплатные.

DDR и PCIe контроллеры бесплатные.

+1

.

0

Я изучил атмеги уже вдоль и поперёк, но после прочтения статьи так и не понял, с чем же мне предстоит столкнуться. Хотелось бы поподробнее узнать о принципах программирования ПЛИСов, о принципиальных отличиях от микроконтроллеров в этом плане. В тексте говорится про какие-то «ячейки», но не поясняется, что же имеется в виду. Вроде как статья ориентирована на чайников вроде меня, но я ничего не понял.

0

Я считаю, что мало начать теоретическое изучение ПЛИС, будет лучше, когда рядом есть отладочная плата и необходимость в создании какого-нибудь проекта. Агитирую купить плату из тех, что представлены выше, или другую. Для ПЛИС это не очень принципиально, но лучше, когда «ячеек» больше.

С чем придется столкнуться? Для меня было несколько сюрпризов и потрясений. Часть из проблем удалось преодолеть только благодаря наличию отладочной платы. Ну и она еще как мотивация: лежит, требует, чтоб с ней что-то сделали. Самый, пожалуй, тяжелый момент, что текст на Verilog это не программа, а скорее описание схемы. Но в процессе чтения книг выяснилось, что есть оператор # чтоб выставить задержку. Например

То есть на линии CLK мы выставили 0, подождали 10тиков, выставили 1. Чудеса! Всю логику можно так описать, причем проще и быстрее, чем на МК. И в эмуляторе все отрабатывает… А в том и дело, что оно только для эмулятора и делается, для отладки, и работает только в нем. В железо он не синтезируется. А я вот надеялся, думал генератор туда заводится как раз для этого. Это одно из самых больших разочарований. Глупость? Но я не один такой, который хотел залить # в железо (пруф потерял, но люди спрашивают). Поэтому там все процессы, растянутые во времени, нужно делать через счетчики-делители частоты, стейт-машины.

С чем придется столкнуться? Для меня было несколько сюрпризов и потрясений. Часть из проблем удалось преодолеть только благодаря наличию отладочной платы. Ну и она еще как мотивация: лежит, требует, чтоб с ней что-то сделали. Самый, пожалуй, тяжелый момент, что текст на Verilog это не программа, а скорее описание схемы. Но в процессе чтения книг выяснилось, что есть оператор # чтоб выставить задержку. Например

CLK = 0;

#10;

CLK = 1;

#10;

CLK = 0;

То есть на линии CLK мы выставили 0, подождали 10тиков, выставили 1. Чудеса! Всю логику можно так описать, причем проще и быстрее, чем на МК. И в эмуляторе все отрабатывает… А в том и дело, что оно только для эмулятора и делается, для отладки, и работает только в нем. В железо он не синтезируется. А я вот надеялся, думал генератор туда заводится как раз для этого. Это одно из самых больших разочарований. Глупость? Но я не один такой, который хотел залить # в железо (пруф потерял, но люди спрашивают). Поэтому там все процессы, растянутые во времени, нужно делать через счетчики-делители частоты, стейт-машины.

0

о принципиальных отличиях от микроконтроллеров в этом плане

Тут проще написать сходства.

1. И то и другое цифровые устройства.

2. И то и другое можно программировать.

Дальше сплошные отличия:

1. В микроконтроллер заливается программа, которая потом инструкция за инструкцией выполняется CPU контроллера. В ПЛИС заливается конфигурация которая коммутирует блоки внутри ПЛИС, и соответственно работает уже в соответствии с тем что туда залили.

2. Микроконтроллер состоит их разных частей: ядро, память, переферия. ПЛИС набор однородных «ячеек» иногда бывают «спецблоки» типа PLL.

3. Микроконтроллеры разных производителей и даже разным моделей одного производителя могут отличаться ядром, периферией, количеством памяти итд. ПЛИС отличается количеством доступных «ячеек» (ну и если копнуть глубже то их структурой но для VHDL/Verilog это пофиг).

ПЛИС в итоге более низкий уровень чем микроконтроллер. При этом на микроконтроллере вы не сможете повторить функционал ПЛИС, а вот наоборот легко. Причём вы можете это сделать по своему усмотрению например надо вам 15 UART вы ставить ядро допустим AVR и навешиваете на него 15 UART. Или допустим захотелось вам MII преобразовать в SPI, вы не описываете как принять кадр потом как его послать по SPI, причём вы описываете это на уровне схемы, прелесть в том что когда вам понадобится 10 таких преобразователей то вы просто 10 раз подключаете модуль преобразования, главное чтобы хватило ног, и они все работают паралельно, а в микроконтроллере вы бы уперлись в его частоту.

PS. Проще побаловаться с симулятором в Quartus например, многое может стать понятней, хотя он и не очень дружелюбен.

+5

ячейки — это некоторые универсальные изолированные схемы которые имеют определенную конфигурацию и подключаются к шинам входных сигналов и выходных.

Конфигурируя подключения входов и выходов этих ячеек мы делаем физическую схему с необходимой нам функцией связывающей вход и выход или какие-то внутренние связи между ячейками или самой же ячейкой. Как правило, ядром ячейки является JK-триггер который можно сконфигурировать в различных вариантах — синхронный, асинхронный, счётный и т.д.

Собственно программирование ПЛИС сводится к написанию функций которые потом переводятся в набор связей между ячейками — это и является «прошивкой» ПЛИС.

Иногда, кстати, сталкиваешься с ситуацией что компилятор не может синтезировать схему — хоть ячеек и хватает но может не хватить внутренних связей между ячейками для синтеза схемы. Если не ошибаюсь, в типичной ПЛИС на 64 ячейки возможны всего 32 внутренние связи — т.е. тупо сделать счетчик на 64 бита не получится. В больших ПЛИС ячейки входят в состав макроячеек, внутри которых действует ограничение на количество внутренних связей и соответственно связей макроячеек с другими макроячейками.

Это конечно вариант простейшей ПЛИС, есть и гибридные ПЛИС в которых включены не только однотипные ячейки, но так же и аппаратные реализации некоторых сущностей — например готовый массив многопортовой RAM, синтезаторы частот, даже иногда микропроцессоры(хотя тут скорей наоборот, в некоторых микропроцессорах есть встроенная обвязка в виде ПЛИС что позволяет реализовать любую необходимую аппаратную периферию прямо на ходу).

Конфигурируя подключения входов и выходов этих ячеек мы делаем физическую схему с необходимой нам функцией связывающей вход и выход или какие-то внутренние связи между ячейками или самой же ячейкой. Как правило, ядром ячейки является JK-триггер который можно сконфигурировать в различных вариантах — синхронный, асинхронный, счётный и т.д.

Собственно программирование ПЛИС сводится к написанию функций которые потом переводятся в набор связей между ячейками — это и является «прошивкой» ПЛИС.

Иногда, кстати, сталкиваешься с ситуацией что компилятор не может синтезировать схему — хоть ячеек и хватает но может не хватить внутренних связей между ячейками для синтеза схемы. Если не ошибаюсь, в типичной ПЛИС на 64 ячейки возможны всего 32 внутренние связи — т.е. тупо сделать счетчик на 64 бита не получится. В больших ПЛИС ячейки входят в состав макроячеек, внутри которых действует ограничение на количество внутренних связей и соответственно связей макроячеек с другими макроячейками.

Это конечно вариант простейшей ПЛИС, есть и гибридные ПЛИС в которых включены не только однотипные ячейки, но так же и аппаратные реализации некоторых сущностей — например готовый массив многопортовой RAM, синтезаторы частот, даже иногда микропроцессоры(хотя тут скорей наоборот, в некоторых микропроцессорах есть встроенная обвязка в виде ПЛИС что позволяет реализовать любую необходимую аппаратную периферию прямо на ходу).

0

В двух словах, ПЛИС это конструктор. Прошивка (программа) для ПЛИС это не ассемблерный код, это всегда схемотехника, просто её вы не рисуете, а описываете на Verilog, VHDL, AHDL. Прошивку для ПЛИС вы можете не писать, а нарисовать в схематике. И как написано, вы можете на ПЛИС создать микроконтролёр, или прошить готовый например, NIOS под Altera… И далее под NIOS вы можете писать ассемблерный код.

0

А я вот почитал книгу Digital Design and Computer Architecture и почти сразу понял, почему я хочу Verilog, а не VHDL: потому что на нём нужно писать меньше букв!

+1

Из плат советую платы фирмы terasic, серия DE. Сам себе взял DE1-SoC. ПЛИС нужно использовать, там где нужна параллельная обработка или не стандартные задачи. Я бы посоветовал использовать их в задачах обработки сигналов, например.

+1

А есть какая-нибудь платка, с которой можно начать работать не устанавливая громозкого проприетарного софта? В идеале пользуясь только тем, что устанавливается через apt-get и не требует действий по получению лицензий?

0

К сожалению, без проприетарного софта в мире FPGA у Вас ничего нормального сделать не получится.

Можете посмотреть на iverilog.icarus.com

Но это только на «поиграться».

Можете посмотреть на iverilog.icarus.com

Но это только на «поиграться».

0

Спасибо за статью! Зашла сюда после того, как увидела в одной из приглянувшихся мне компаний вакансию на разработчика ПЛИС, до этого вообще не слышала про HDL-языки и из подобного щупала с матом ассемблер. Да и из технического бэкграунда пайка и веб-вёрстка. Как думаете, стоит ли попробовать освоить что-то из HDL? И сколько вообще платят за разработку ПЛИС?

0

Зарегистрируйтесь на Хабре, чтобы оставить комментарий

Публикации

Изменить настройки темы

Сделай шаг к ПЛИС