Здравствуйте, Хабросообщество.

Хотел бы поделиться с Вами решением одной проблемы, с которой столкнулся и которую решал довольно долго. Причем помочь решить эту проблему не смогли куча различных радиоэлектронщиков (к которым я обращался за помощью и консультацией), а также 2 отечественных и 1 иностранный форумы по радиоэлектронике.

Я хочу сделать так, чтобы тот, кто это прочитает, никогда не «встал на грабли», на которые я встал и с которыми долго мучался.

Проблема была в том, что я не мог использовать более 1 пина на одном IDC разъеме. Если на разъеме использовалось более 1 пина (2 и более) — то при проверке осциллографом разъем молчал.

Как выяснилось теперь — проблема заключалась в правилах наименования в Quartus II при использовании Schematic.

Всем тем, кому это будет полезно или интересно — прошу под кат.

С данной проблемой сталкивался и на целевых (handmade) устройствах. Но для наглядности хотел бы продемонстрировать на ките Altera DE1 (Рисунок 1).

Рис. 1 — Altera DE1 Development and Education Board

Загрузил в Quartus II файл «Altera_DE1_pin_assignments.csv» с назначениями пинов ПЛИС (Имя в проекте — Номер пина ПЛИС), который взял с диска от кита.

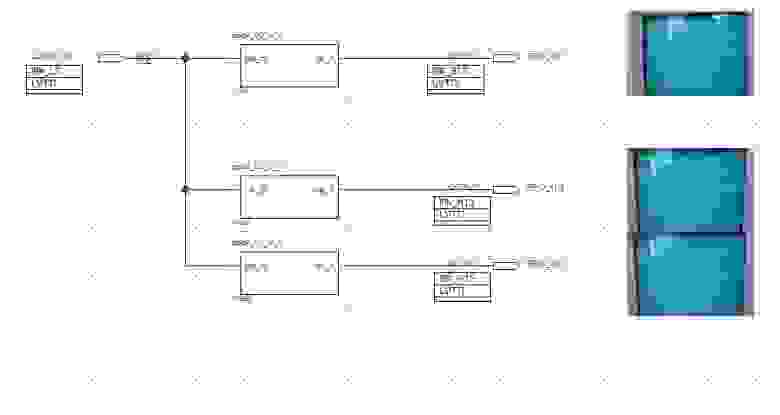

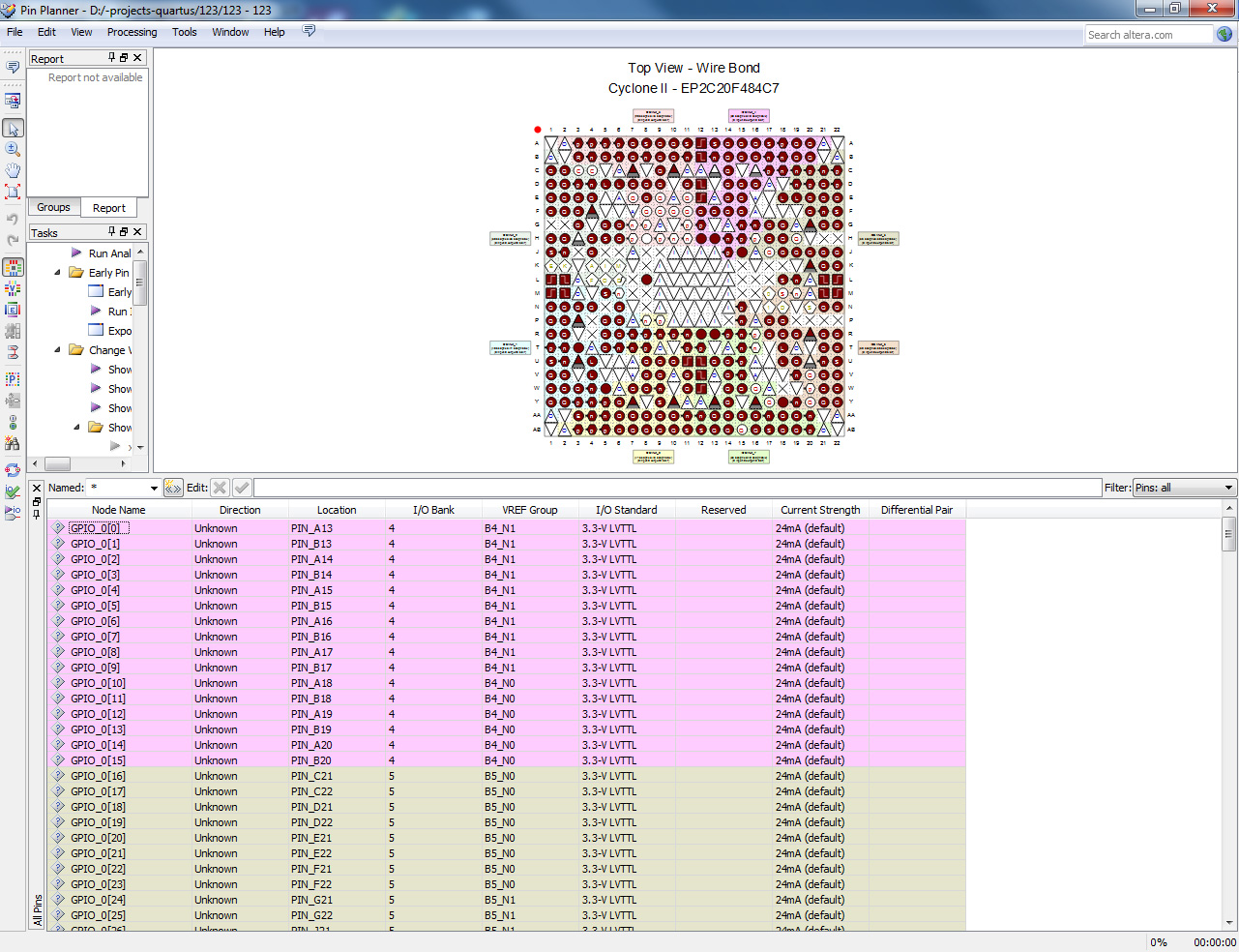

На рисунке 2 вы можете увидеть имена пинов сорока-пинового IDC разъема «GPIO_0» в Pin Planner.

Рис. 2 — Quartus II Pin Planner for Altera DE1

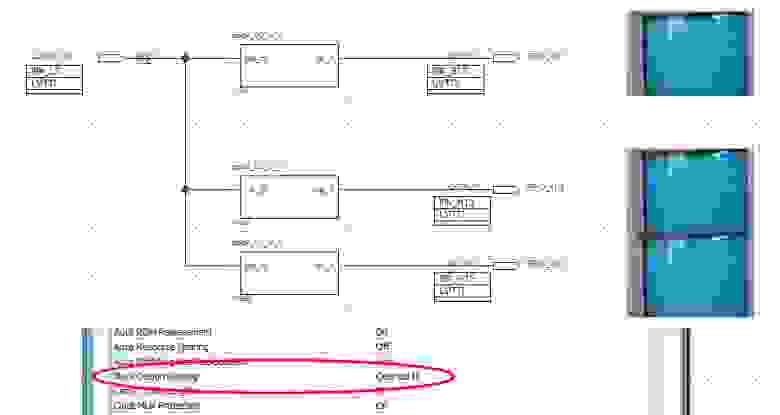

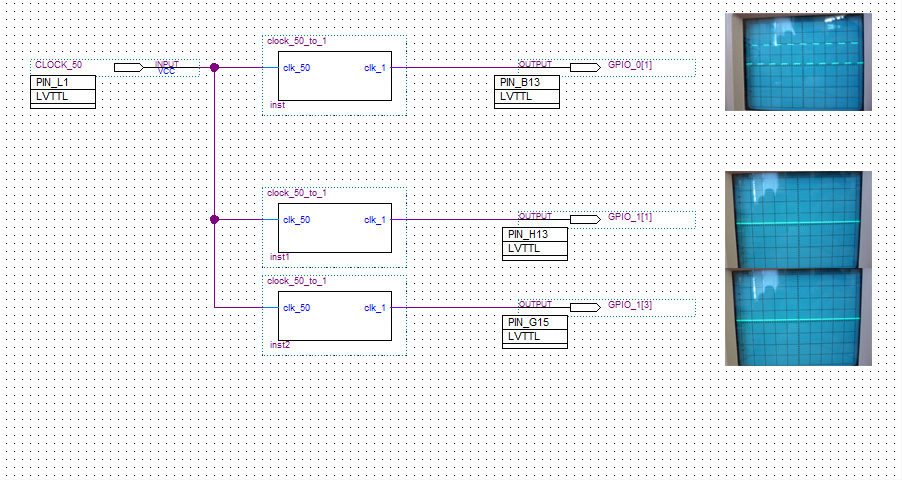

Для наглядности более подробно опишу проблему на проекте, показанном на рисунке 3. С пина «CLOCK_50» приходит клок 50 МHz (от тактового генератора на ките, который подключен к определенному пину ПЛИС). «clock_50_to_1» — рукописный модуль на языке Verilog, который преобразует клок 50 МHz в 1 МHz посредством счетчика (аналогичные проблемы наблюдались и при использовании встроенной в Quartus II мегафункции ALTPLL). Преобразованный клок выводится на 2 IDC разъема — GPIO_0 и GPIO_1. На разъеме GPIO_0 используется 1 пин ([1]) и все работает, на разъеме GPIO_1 используется 2 пина ([1],[3]) и сигнала нет.

Рис. 3 — Скриншот Quartus II и фото с осциллографа

Один из пользователей форума Altera Forum, заметил «краем глаза» какие-то странные предупреждения при компиляции проекта (который показан на рисунке 3) в Quartus II, и сказал: «Я с этим не сталкивался, что делать не знаю, но советую вам делать модуль верхнего уровня проекта не в schematic, а на языке Verilog или VHDL».

Одним словом, проанализировав предупреждения, стало понятно, что Quartus II переименовывает

«GPIO_1[1]» в «GPIO_11»

«GPIO_1[3]» в «GPIO_13»

А для имен GPIO_11 и GPIO_13 конкретные пины ПЛИС не назначены.

Итак мы выяснили, что существует две схемы переименования — Max+Plus II и Quartus II.

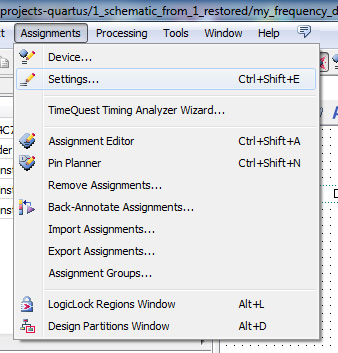

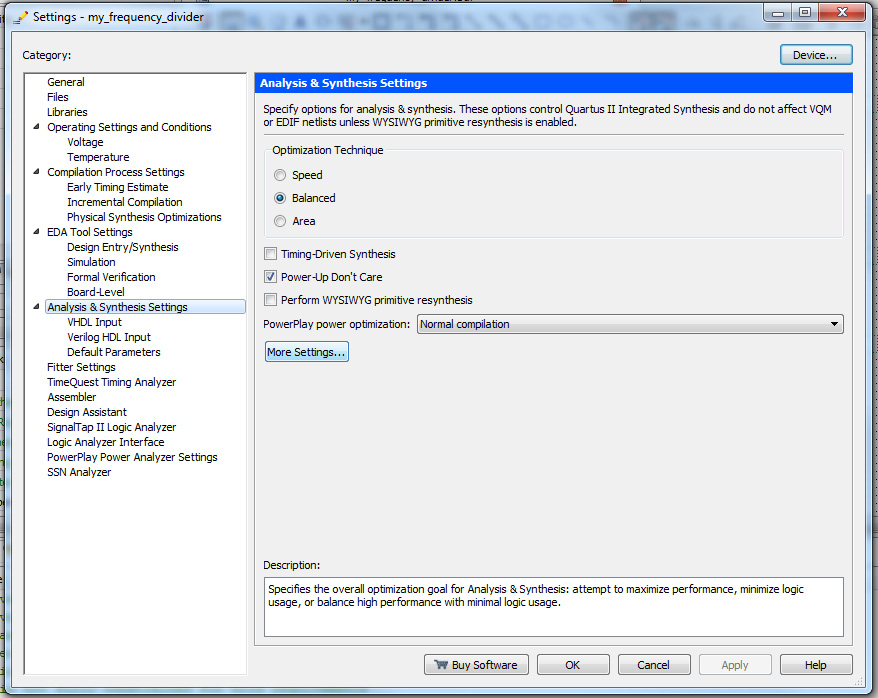

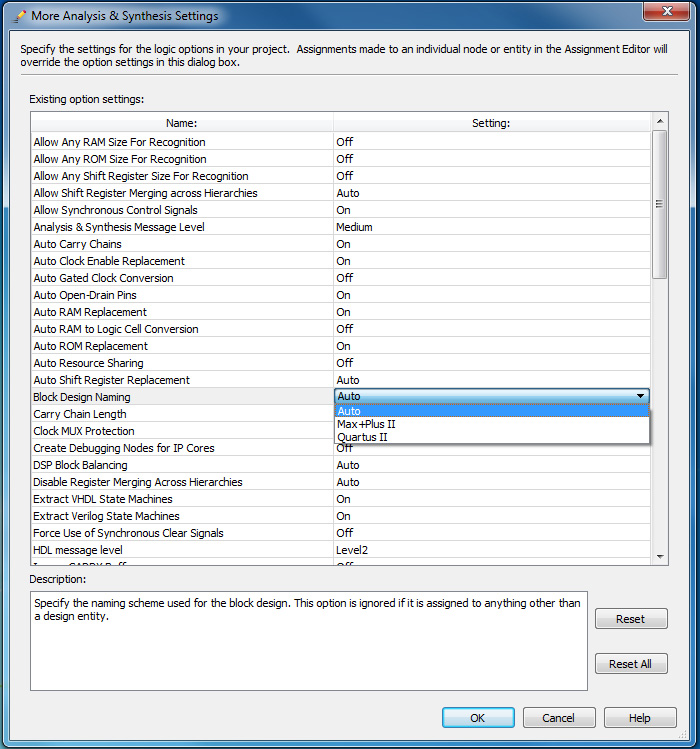

Для проекта можно явно переключать эти схемы правил наименования:

Assignments => Settings => Analysis & Synthesis Settings => More Settings => Block Design Naming

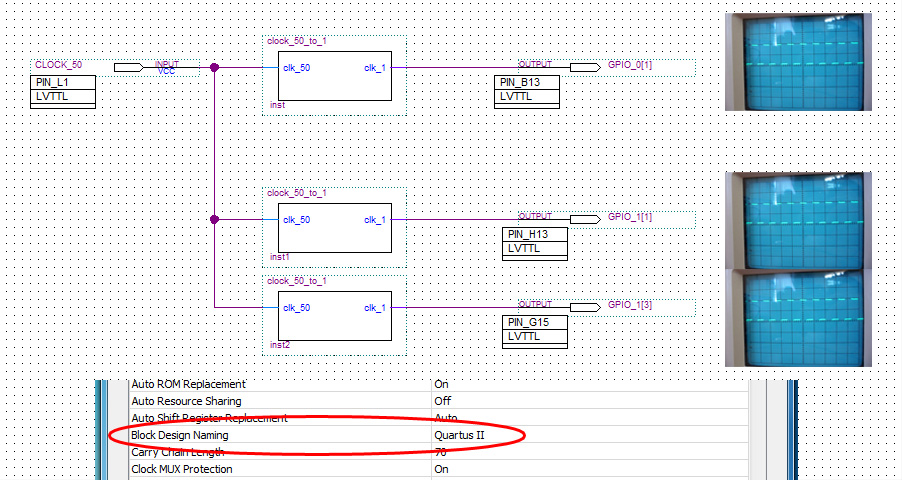

Как видно из рисунка 4, если явно переключить схему переименования на Quartus II, то проблема решается.

Рис. 4 — Скриншот Quartus II и фото с осциллографа

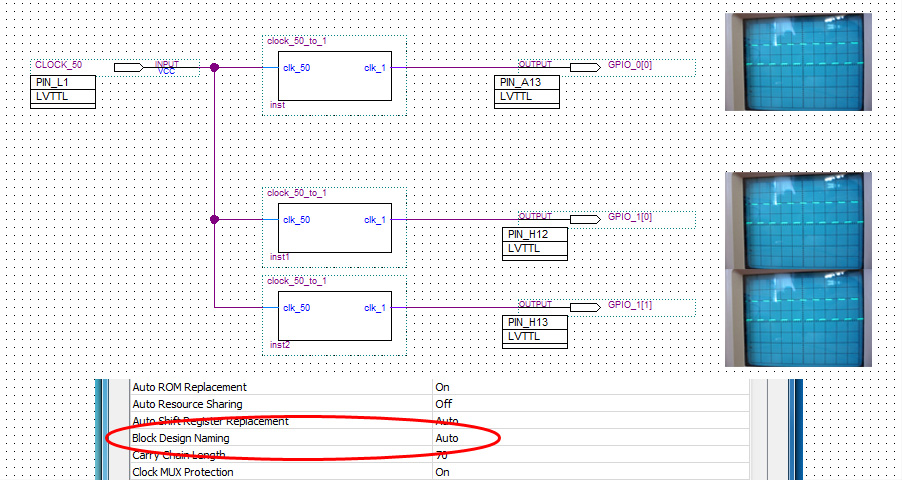

Если начать использовать пины IDC разъема по порядку (от 0 до n), то даже при выставленной схеме переименования Auto, Quartus II не будет ничего переименовывать.

Рис. 5 — Скриншот Quartus II и фото с осциллографа

P.S. Я буду очень рад, если смогу облегчить кому-то жизнь и съэкономить его время.

Хотел бы поделиться с Вами решением одной проблемы, с которой столкнулся и которую решал довольно долго. Причем помочь решить эту проблему не смогли куча различных радиоэлектронщиков (к которым я обращался за помощью и консультацией), а также 2 отечественных и 1 иностранный форумы по радиоэлектронике.

Я хочу сделать так, чтобы тот, кто это прочитает, никогда не «встал на грабли», на которые я встал и с которыми долго мучался.

Проблема была в том, что я не мог использовать более 1 пина на одном IDC разъеме. Если на разъеме использовалось более 1 пина (2 и более) — то при проверке осциллографом разъем молчал.

Как выяснилось теперь — проблема заключалась в правилах наименования в Quartus II при использовании Schematic.

Всем тем, кому это будет полезно или интересно — прошу под кат.

Демонстрация проблемы

С данной проблемой сталкивался и на целевых (handmade) устройствах. Но для наглядности хотел бы продемонстрировать на ките Altera DE1 (Рисунок 1).

Рис. 1 — Altera DE1 Development and Education Board

Загрузил в Quartus II файл «Altera_DE1_pin_assignments.csv» с назначениями пинов ПЛИС (Имя в проекте — Номер пина ПЛИС), который взял с диска от кита.

На рисунке 2 вы можете увидеть имена пинов сорока-пинового IDC разъема «GPIO_0» в Pin Planner.

Рис. 2 — Quartus II Pin Planner for Altera DE1

Для наглядности более подробно опишу проблему на проекте, показанном на рисунке 3. С пина «CLOCK_50» приходит клок 50 МHz (от тактового генератора на ките, который подключен к определенному пину ПЛИС). «clock_50_to_1» — рукописный модуль на языке Verilog, который преобразует клок 50 МHz в 1 МHz посредством счетчика (аналогичные проблемы наблюдались и при использовании встроенной в Quartus II мегафункции ALTPLL). Преобразованный клок выводится на 2 IDC разъема — GPIO_0 и GPIO_1. На разъеме GPIO_0 используется 1 пин ([1]) и все работает, на разъеме GPIO_1 используется 2 пина ([1],[3]) и сигнала нет.

Рис. 3 — Скриншот Quartus II и фото с осциллографа

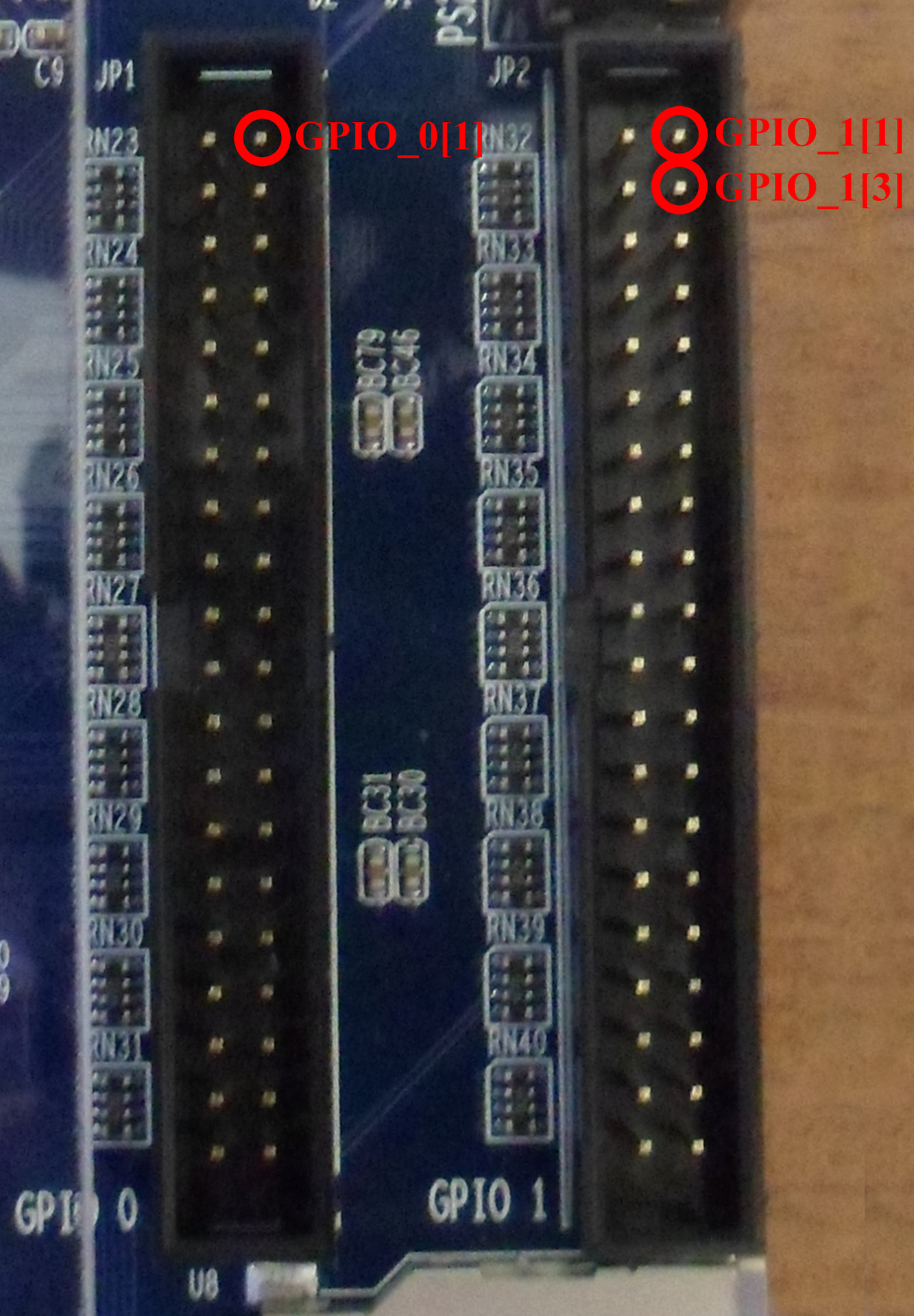

Для наглядности на рисунке в спойлере приведена фотография разъемов:

Причина проблемы

Один из пользователей форума Altera Forum, заметил «краем глаза» какие-то странные предупреждения при компиляции проекта (который показан на рисунке 3) в Quartus II, и сказал: «Я с этим не сталкивался, что делать не знаю, но советую вам делать модуль верхнего уровня проекта не в schematic, а на языке Verilog или VHDL».

Текст предупреждений следующий:

Warning (275080): Converted elements in bus name «GPIO_1» using legacy naming rules. Make any assignments on the new names, not on the original names.

Предупреждение (275080): Преобразованные элементы в шине с именем «GPIO_1» используют унаследованные правила наименования. Сделайте любые назначения для новых имен, не для исходных имен.

— Warning (275081): Converted element name(s) from «GPIO_1[1]» to «GPIO_11»

— Предупреждение (275081): Преобразование имени элемента из «GPIO_1[1]» в «GPIO_11»

— Warning (275081): Converted element name(s) from «GPIO_1[3]» to «GPIO_13»

— Предупреждение (275081): Преобразование имени элемента из «GPIO_1[3]» в «GPIO_13»

Critical Warning (169085): No exact pin location assignment(s) for 2 pins of 4 total pins

Предупреждение особой важности (169085): Не назначено точное расположение пина(ов) для 2 пинов из 4 пинов в общем

— Info (169086): Pin GPIO_11 not assigned to an exact location on the device

— Информация (169086): Не назначено точное расположение пина GPIO_11 на устройстве

— Info (169086): Pin GPIO_13 not assigned to an exact location on the device

— Информация (169086): Не назначено точное расположение пина GPIO_13 на устройстве

Предупреждение (275080): Преобразованные элементы в шине с именем «GPIO_1» используют унаследованные правила наименования. Сделайте любые назначения для новых имен, не для исходных имен.

— Warning (275081): Converted element name(s) from «GPIO_1[1]» to «GPIO_11»

— Предупреждение (275081): Преобразование имени элемента из «GPIO_1[1]» в «GPIO_11»

— Warning (275081): Converted element name(s) from «GPIO_1[3]» to «GPIO_13»

— Предупреждение (275081): Преобразование имени элемента из «GPIO_1[3]» в «GPIO_13»

Critical Warning (169085): No exact pin location assignment(s) for 2 pins of 4 total pins

Предупреждение особой важности (169085): Не назначено точное расположение пина(ов) для 2 пинов из 4 пинов в общем

— Info (169086): Pin GPIO_11 not assigned to an exact location on the device

— Информация (169086): Не назначено точное расположение пина GPIO_11 на устройстве

— Info (169086): Pin GPIO_13 not assigned to an exact location on the device

— Информация (169086): Не назначено точное расположение пина GPIO_13 на устройстве

Одним словом, проанализировав предупреждения, стало понятно, что Quartus II переименовывает

«GPIO_1[1]» в «GPIO_11»

«GPIO_1[3]» в «GPIO_13»

А для имен GPIO_11 и GPIO_13 конкретные пины ПЛИС не назначены.

Что по этому поводу сказано в базе знаний Altera:

Программное обеспечение Max+Plus II имеет ограниченную поддержку для имен шин в схематике и будет иногда переименовывать элементы в шине, чтобы работать в пределах этих ограничений.

Например программное обеспечение Max+Plus II переименовало бы имена шин a[1..0], b[1], b[0] в a1, a0, b1, b0 соответственно.

Программное обеспечение Quartus II первоначально сохраняло такое поведение для обратной совместимости, но теперь поддерживает способ, который сохраняет естественные имена шин (с квадратными скобками) в Вашем проекте.

Однако, чтобы избежать изменения поведения программного обеспечения для существующих проектов, Quartus II продолжает использовать более старые соглашения обозначения для наследования BDF (Block Design File) и GDF (Graphic Design File) файлов проекта.

Для нового схематика программное обеспечение Quartus II сохраняет настоящие имена (с квадратными скобками) в проекте во время компиляции.

Правила наименования для Quartus II версии 7.1 and более ранних версий:

(СХЕМА ПЕРЕИМЕНОВАНИЯ Max+Plus II):

Если шина a[0..3] разбивается на части, то создаются 4 пина: a0, a1, a2, a3

Правила наименования для Quartus II версии 7.2 and более поздних версий:

(СХЕМА ПЕРЕИМЕНОВАНИЯ Quartus II):

Если шина a[0..3] разбивается на части, то создаются 4 пина: a[0], a[1], a[2], a[3]

Например программное обеспечение Max+Plus II переименовало бы имена шин a[1..0], b[1], b[0] в a1, a0, b1, b0 соответственно.

Программное обеспечение Quartus II первоначально сохраняло такое поведение для обратной совместимости, но теперь поддерживает способ, который сохраняет естественные имена шин (с квадратными скобками) в Вашем проекте.

Однако, чтобы избежать изменения поведения программного обеспечения для существующих проектов, Quartus II продолжает использовать более старые соглашения обозначения для наследования BDF (Block Design File) и GDF (Graphic Design File) файлов проекта.

Для нового схематика программное обеспечение Quartus II сохраняет настоящие имена (с квадратными скобками) в проекте во время компиляции.

Правила наименования для Quartus II версии 7.1 and более ранних версий:

(СХЕМА ПЕРЕИМЕНОВАНИЯ Max+Plus II):

Если шина a[0..3] разбивается на части, то создаются 4 пина: a0, a1, a2, a3

Правила наименования для Quartus II версии 7.2 and более поздних версий:

(СХЕМА ПЕРЕИМЕНОВАНИЯ Quartus II):

Если шина a[0..3] разбивается на части, то создаются 4 пина: a[0], a[1], a[2], a[3]

Путь решения проблемы №1

Итак мы выяснили, что существует две схемы переименования — Max+Plus II и Quartus II.

Для проекта можно явно переключать эти схемы правил наименования:

Assignments => Settings => Analysis & Synthesis Settings => More Settings => Block Design Naming

Для наглядности в спойлере скриншоты переключения правил переименования по шагам:

Как видно из рисунка 4, если явно переключить схему переименования на Quartus II, то проблема решается.

Рис. 4 — Скриншот Quartus II и фото с осциллографа

Путь решения проблемы №2

Если начать использовать пины IDC разъема по порядку (от 0 до n), то даже при выставленной схеме переименования Auto, Quartus II не будет ничего переименовывать.

Рис. 5 — Скриншот Quartus II и фото с осциллографа

Для наглядности на рисунке в спойлере приведена фотография разъемов:

P.S. Я буду очень рад, если смогу облегчить кому-то жизнь и съэкономить его время.