Статья про то, как из недорогой отладочной платы OMDAZZ c ПЛИС CycloneIV EP4CE6 получить ретро-компьютер с монитором, клавиатурой и тетрисом, но с современным процессором на базе RSIC-V и компилятором GCC.

Программируемые логические интегральные схемы

Статья про то, как из недорогой отладочной платы OMDAZZ c ПЛИС CycloneIV EP4CE6 получить ретро-компьютер с монитором, клавиатурой и тетрисом, но с современным процессором на базе RSIC-V и компилятором GCC.

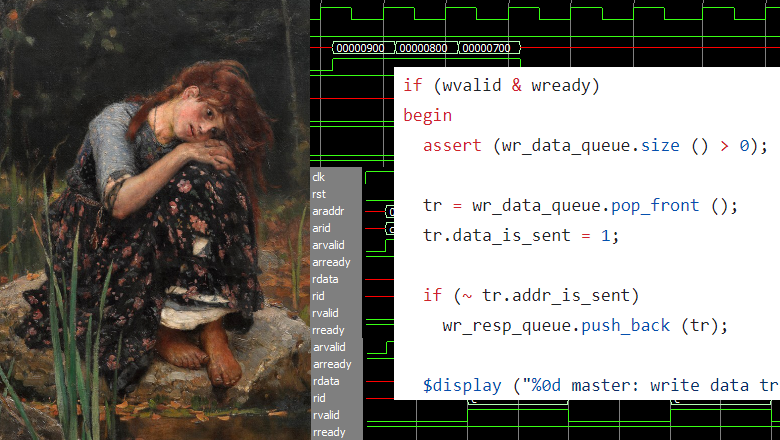

Сейчас я интервьирую кандидатов которые приходят на позиции в RTL design / проектировщики микросхем на уровне регистровых передач. Но 5 лет назад я интервьировал студентов и других инженеров на позиции в DV / Design Verification / верификаторы блоков микросхем.

Моим стандартным вопросом было написать маркером на доске псевдокод для упрощенного драйвера модели шины (Bus Functional Model - BFM) для протокола AXI. На этом вопросе у ~80% кандидатов наступала агония - они как ужи на сковородке пытались натянуть сову на глобус - приспособить решение для последовательной шины а-ля APB, которое они прочитали в каком-нибудь тьюториале - к шине AXI, которая во-первых конвейерная, а во-вторых, допускает внеочередные ответы на запросы чтения с разными идентификаторами.

Аналогия из другой области: представьте, что кто-то пытается обходить дерево или решить "ханойские башни" - не зная концепций рекурсии и стека. Или написать GUI интерфейс, не зная концепции cобытийно-ориентированной архитектуры.

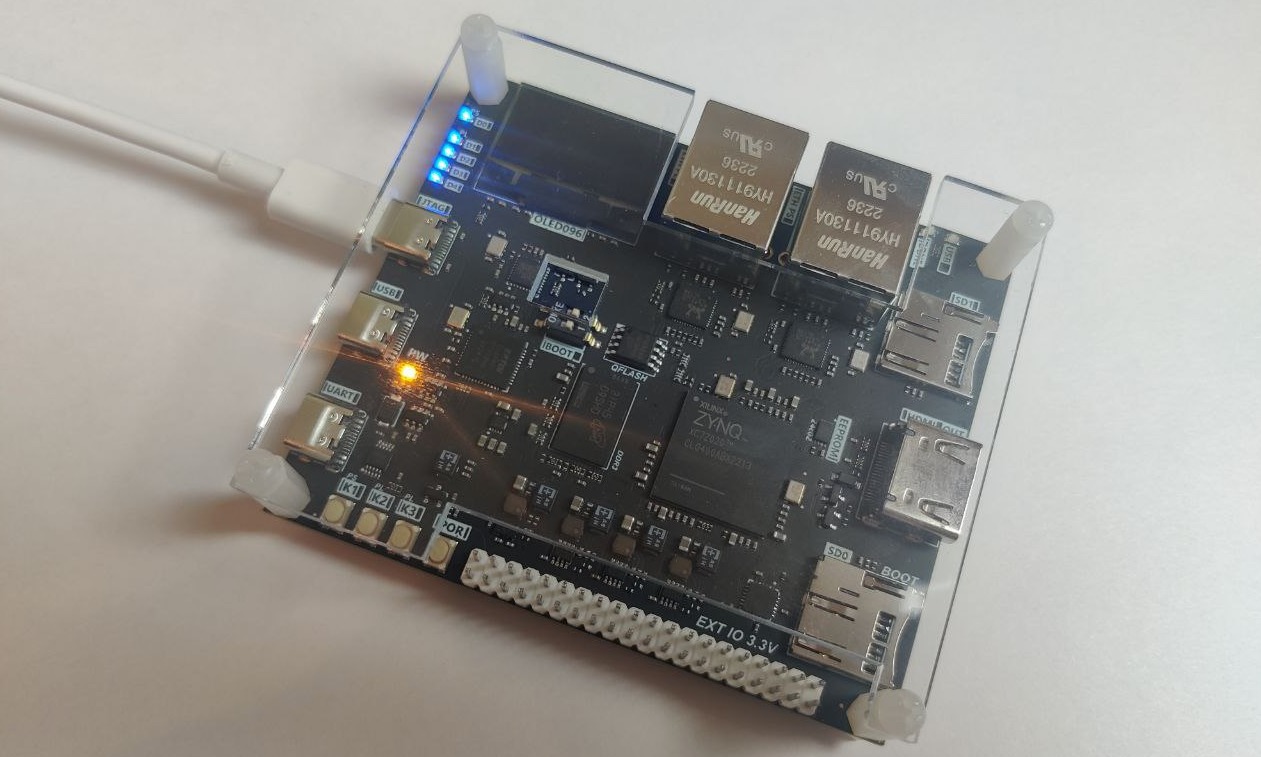

После написания последнего обзора на новую отладку Я не смог удержаться от того, чтобы не сделать простую проверку работоспособности платы, т.к. очень не хотелось бы напороться на какие-либо проблемы во время решения сложной задачи. Поэтому решил сделать простую мигалку светодиодами и задействовать, плюсом к этому, кнопки на плате. Немного поразмыслив, Я решил, что обычный “ногодрыг” на Verilog - это уже не так интересно и мне показалось, что лучше сделать это с помощью AXI GPIO и своего IP-ядра, инициировав экшн из baremetal-приложения. В общем, кому интересно, заглядывайте в статью, там Я описал, как добавить свое кастомное AXI Peripheral IP-ядро, как правильно организовать проект и обратиться к GPIO для чтения и записи логического уровня. Поехали…

Все знают про язык программирования C, поменьше — про язык программирования F, кое‑кто про B, предшественник C, а вот знаете ли вы про язык «e»? Их кстати два — один с большой буквы «E», а другой с маленькой «e».

Вы наверное подумали, что это еще один безызвестный язык от какого‑нибудь аспиранта провинциального европейского университета. Однако интерпретатор маленького «e» под названием Specman продали в 2005 году большой компании Cadence Design Systems за $315 милионов долларов. Причем президента продающей компании Verisity звали Гаврилов. Также можно нагуглить, что этот язык использовали внутри компании Intel. Что же в нем такого, что вызвало интерес у толстых богатых корпораций?

ПЛИС-культ привет, FPGA хаб!

В очередной раз мы собираемся нашим ламповым FPGA комьюнити для обмена опытом, всякими премудростями и просто для общения в кругу таких же ПЛИСоводов как и ты.

Программа уже сформирована, регистрация открыта и возможно тебе повезет стать частью фактически единственного FPGA движа на постсоветском пространстве. Не откладывай на завтра и регистрируйся на IV конференцию FPGA-Systems 2023.1.

Однажды, вечером, в очередной раз прочитывая чатик в телеграмме по теме Embedded + FPGA, я увидел обсуждение очередной отладочной платы с Zynq 7000 на борту. Описание выглядело очень любопытно. Полистав документацию на плату, посмотрев описание - я заинтересовался еще больше, вспомнил сразу про ограничения платы QMTech и понял, что данная отладка лишена всех тех недостатков, что были у QMTech. Сразу в голове созрел контент-план и понимание того, что изучая возможности этой платы можно написать много интересных статей для новичков :) Я тут же заказал эту плату, и решил, что пришло время вернуться к изучению возможностей отладочных плат с Zynq. И первым шагом на пути моего возвращения в написание статей я решил сделать небольшой обзор этой платы с рассказом о том, почему она меня заинтересовала, и что в ней интересного. Всем любопытным - добро пожаловать!

Однажды мне не спалось ночью и я залип на сайтах про паяльники. Возникло желание купить и сразу появились вопросы: на сколько ватт? Не больше 30? А почему большинство на 60-80 ватт? 60/40 олово свинец? А почему куча паяльных станций идут в комплекте с lead-free проводами припоя? Канифоль сейчас внутри проводов? А почему есть и провода припоя без канифоли? Бронзовую мочалку для очистки? А почему столько комплектов с и белой и бронзовой?

Вспомнил и повод, чтобы научиться паять. Когда-то Руслан Тихонов, руководитель кружка из Москвы, говорил мне что хочет сделать простые упражнения на платах ПЛИС для школьников. Как часть триады "микросхемы малой степени интеграции - ПЛИС - Ардуино". По этому поводу я купил самую дешевую плату с CPLD Altera MAX II (ныне это Intel FPGA), но обнаружил что у нее не припаян переходник.

Я выставил вопросы по паяльники на фейсбук и после оживленной дискуссии мой приятель Денис Никитин вызвался научить меня паять как полагается. Денис работает проектировщиком печатных плат в компании Zoox, ныне часть компании Amazon. Zoox делает беспилотные автомобили, то есть Денис на передовом рубеже паятельного прогресса. Я заснял мастер-класс от Дениса на видео:

Вчера у меня в ленте на фейсбуке (жаль что в закрытом посте) проявился еще один аспект ChatGPT, жуть которого я не вполне осознавал. Представьте, что ваш менеджер присылает вам емейл: "я вот тут сгенерил с помощью ChatGPT код на языке описания аппаратуры SystemVerilog, который реализует мою идею, ты его поправь немного и в продакшн, а то нас сроки поджимают".

Почему это жутко? Потому что в обсуждаемом посте ChatGPT сгенерил так называемый несинтезируемый код. Это означает: код вроде и есть, и после массажирования даже будет компилироваться в симуляторе, но вот чип из него сделать нельзя. Никак, вообще никак. Для решения этой задачи нужно написать совсем другой код, у которого не будет ни одной строчки общего с тем, что прислал менеджер.

То есть менеджер думает, что вместе с ChatGPT сделал за вас 90% работы, а на самом деле.

У разных электронных компаний вопросы на интервью немного отличаются. В одной интервьюер на скрининге (первом интервью) спросит кандидата на RTL позицию про конечный автомат, в другой про арбитр, кэш или конвейер, в третьей про упорядочение неупорядоченных транзакций. Но на большом интервью вопрос про очередь FIFO появится практически всегда - не первым/вторым, но третьим.

Это может быть элементарный вопрос "напишите на доске (физической, ха-ха, без доступа к интернету и ChatGPT) код для FIFO на D-триггерах". Или это может быть обсуждение микроархитектуры какого-нибудь извращенного FIFO, например FIFO с отменой вталкиваний, или с возможностью втолкнуть и вытолкнуть переменное количество кусков данных за такт, или с конвейером и кредитным счетчиком, или работающее на памяти с высокой латентностью, или асинхронное FIFO из статьи Клиффа Каммингса про пересечение тактового домена.

Эта заметка является сиквелом заметки "FIFO для самых маленьких", а также приквелом занятия в Школе синтеза цифровых схем в ближайшую субботу. Главное нововведение - все примеры и упражнения теперь делаются не только в симуляторе, но и на плате ПЛИС.

ПЛИС-культ привет, FPGA хаб!

Давненько я не писал полноценных статей на хабре, всё больше как-то занимался организацией FPGA движа: всякими там новостными подборками, ютуб стримами по FPGA, организацией плисовых конференций и много чем другим.

Но всё новое — хорошо забытое старое, поэтому решил изложить в текстовом виде несколько идей, которые легли в основу стримов.

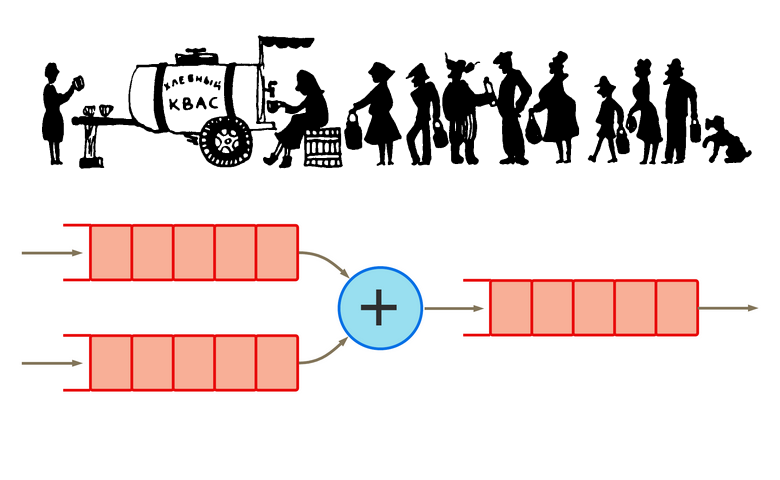

И в этой заметке предлагаю вам погрузиться в небольшое исследование c реализацией конвейеризованного многоразрядного сумматора всего с 1 уровнем логики, эдакого LUTа в сферическом вакууме, идеи которого, я уверен, найдут отклик в исследовательских работах начинающих адептов программируемой логики.

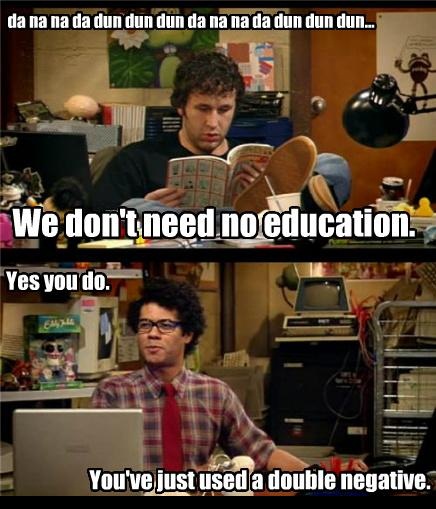

У меня был в свое время практикант из Стенфорда, от которого я получил инсайдерскую информацию, чему их там учат. Потом я интервьировал много студентов, и понял, что если человек не делает самостоятельных проектов в вузе, а просто плывет по течению программы как медуза, то будучи выброшенным на берег индустрии, он становится совершенно беспомощным.

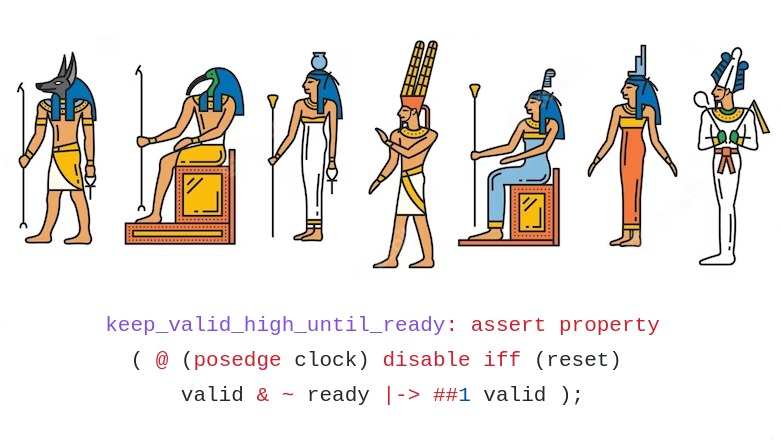

Когда я вижу у недавнего выпускника в резюме какой-то из протоколов в котором используется valid/ready, например AXI или AHB, я прошу его спроектировать блок, у которого на входе два числа A и B, а на выходе их сумма. Разумеется не просто написать SUM=A+B, а еще и поставить valid/ready сигналы на каждый из A, B, SUM, чтобы A и B могли приходить в разное время, а также чтобы блок ждал, если SUM не может быть передана другому блоку сразу.

Некоторые не справляются. Грустно смотреть на человека, который потратил 6 лет своей жизни (4 года в бакалавриате и 2 года в магистратуре) и океан денег на образование - и не может сложить два числа и бьется как угорь на сковородке. То блок не работает когда числа приходят в разное время, то создатель забывает снять valid, и блок на 2+2 выдает не 4, а 4-4-4-4-4-4-4... То числа складываются не попарно, а просто записываются в регистры и на выход идет их текущая сумма, хотя количество аргументов A и B не совпадает. То не отрабатывается backpressure и результаты теряются, то (после того как кандидат написал страницу кода на верилоге) блок работает на половинной производительности, то есть не может принимать поток чисел подряд, а ожидает между ними пропуски (gaps). Короче ведет себя как ChatGPT.

Во всем мире и в нашей стране резко возрос интерес к разработке микроэлектроники, ключевым элементом которой являются системы на кристалле. Разработка этого класса устройств требует глубоких специальных знаний и опыта, а специалистов такого профиля в индустрии не хватает. При этом традиционные способы подготовки дают хорошую фундаментальную базу, но выпускники вузов не обладают необходимым опытом работы в реальных проектах.

В то же время в отрасли немало специалистов с практическим багажом, которые уже решают прикладные задачи проектирования цифровой логики, но в смежных с разработкой ASIC областях — например, FPGA инженеры. Мы заметили, что у нас в компании нередким стал кейс, когда в команду приходят специалисты с опытом в FPGA-разработке, довольно быстро включаются в задачи проектирования ASIC и потом целиком уходят в эту смежную область, ведь маршруты проектирования и инструменты похожи.

Мы решили систематизировать этот опыт и превратить его во внутренний курс переподготовки из FPGA-дизайнеров в ASIC. Если вы тоже задумывались о том, чтобы начать проектировать IP-блоки для ASIC, прочитайте эту статью. Мы поговорили с нашими инженерами, которые самостоятельно прошли путь от цифрового синтеза под FPGA к проектированию ASIC о том, какие знания и опыт для этого нужны, и в чем разница в построении процессов и устройстве работы команд. И, кажется, нашли много плюсов перехода в эту смежную область.

10 лет назад в Санта-Клара, Калифорния, неподалеку от Интела и NVidia, стоял кампус Huawei. В нем работали не только китайцы, но и вообще обычная публика Silicon Valley - индусы, американцы, даже русские попадались. Бизнесмены калифорнийских электронных компаний говорили "Huawei - это дверь в Китай" и заключали с ними крупные сделки.

Но американское правительство Huawei невзлюбило. Можно обсусоливать те или иные поводы, но коренная причина понятна - американскому правительству хочется, чтобы Америка сохраняла технологическое преимущество. Ибо если технология коммодифицируется и айфон не будет ничем особенным, то кто будет читать брошурки про продвижение демократии, распостраняемые американскими посольствами в других странах? Над ними будут просто смеяться.

И вот правительство начало Huawei жучить - и от Андроида отлучило, и от других критических технологий. Но на всяких хитрецов найдется гайка с левой резьбой. И вот что Huawei стал делать по этому поводу.

Обнаружил интересный баг американской системы образования:

У многих студентов в резюме стоит "делал курсовой проект по алгоритму Томасуло, out-of-order суперскаляру, многопоточному процессору итд".

На это я спрашиваю: "Прекрасно, давайте возмем два процессорных ядра - одно со статическим конвейером, а у другого с динамическим, как в вашем курсовике. Насколько ваш процессор будет производительнее?"

На это они отвечают "процессор будет производительнее, потому что" - и начинают ковыряться в деталях зависимостей между инструкциями.

На это я машу руками и говорю "стоп-стоп-стоп. Я не просил вас объяснить мне что такой RaW (read-after-write), WaR и WaW зависимости. Я вообще не спрашивал у вас "почему?" Я спросил у вас "сколько?" Я просил вас грубо оценить пользу от вашей разработки.

Я работаю проектировщиком аппаратного блока графического процессора в телефонах Samsung, в рамках совместного проекта с AMD. Сейчас наш менеджмент расширяет команду и поощряет инженеров распостранять информацию о новых позициях среди своих знакомых. Я решил написать это пост для более широкой аудитории, так как множество людей, способных пройти интервью на RTL или DV позицию - больше, чем множество моих знакомых. Если вы сможете прислать мне ответ на задачку в моем посте вместе с вашим резюме, я перешлю его нанимающему менеджеру и рекрутеру нашей группы (в комментах прошу ответ не писать). Если резюме им понравится, вам нужно будет пройти стандартное собеседование на несколько часов, с несколькими инженерами, у каждого из которых свой набор задачек.

Также я покажу материалы, по которым можно готовиться к собеседованию, особенно если вы студент или у вас ограниченный опыт в микроэлектронной промышлености.

Добрый день! В этой статье я расскажу, как наши заказчики используют ПЛИС в полунатурных стендах и стендовых испытаниях.

В центре инженерных технологий и моделирования «Экспонента» уже много лет мы занимаемся продвижением модельно-ориентированного проектирования в России. Поэтому наш опыт сконцентрирован вокруг инструментов модельно-ориентированного проектирования — то есть различных сред моделирования и симуляции — и применения их в инженерных разработках.

Эта статья написана совместно с нашими хорошими партнерами — компанией «РИТМ». Компания занимается разработкой полунатурных стендов и комплексов полунатурного моделирования «РИТМ» (КПМ «РИТМ»), которые используются нашими заказчиками.

КПМ «РИТМ» представляет собой программно-аппаратное решение для тестирования в реальном времени. Спектр его применений широкий: от быстрого прототипирования алгоритмов управления до полунатурного моделирования объекта управления (Hardware-in-the-Loop или HIL тестирование). РИТМ применяется нашими заказчиками в различных инженерных областях: от авиастроения и ВПК до автомобилестроения и электроэнергетики.

КПМ «РИТМ» поставляется настроенным «под ключ» под задачи проекта или стенда, и оснащен всеми необходимыми модулями ввода-вывода (аналоговыми, цифровыми, специализированными интерфейсами и протоколами). Пользователи могут быстро и бесшовно запускать свои модели в реальном времени (содержащие алгоритмы или модели объекта управления) и подключать их к реальным устройствам (например, блоку управления или исполнительным механизмам) через модули ввода-вывода.

Наши заказчики успешно используют этот подход уже многие годы, но в некоторых узких задачах сталкиваются со следующими проблемами:

• Необходимо существенно сократить шаг расчета алгоритма;

• Не хватает вычислительных ресурсов для решения задачи в реальном времени на процессоре;

• Требуется подключить к алгоритму высокоскоростные цифровые, аналоговые или другие интерфейсы;

• Требуется поддержать заказные интерфейсы или протоколы обмена.

Если вы тоже сталкиваетесь с такими проблемами, то добро пожаловать под кат — даже если вы раньше никогда не слышали о модельно-ориентированном проектировании или ПЛИС.

AMD проводит суперкомпьютерный день в Назарбаевском Университете в Астане, в Казахстане. 29 сентября. Можно подсоединиться по Зуму. Зарегистрироваться можно до 27 сентября по ссылке.

Вообще приезжающие в Астану замечали, что в городе есть амальгамация духа советских городов с духом американского Лас-Вегаса, в частности в элементах архитектуры.

Теперь можно добавить и другое сходство: в Лас-Вегасе помимо казино есть университет, в котором еще в допотопные времена стояли суперкомпьютеры и велись конкурсы на качество распознавания образов. Также там сейчас преподает Сара Харрис, соавтор известного учебника. Кроме этого в Лас-Вегасе иногда проводится конференция DAC по автоматизации проектирования электроники. Почему бы не превратить Астану в евразийский центр такого рода?

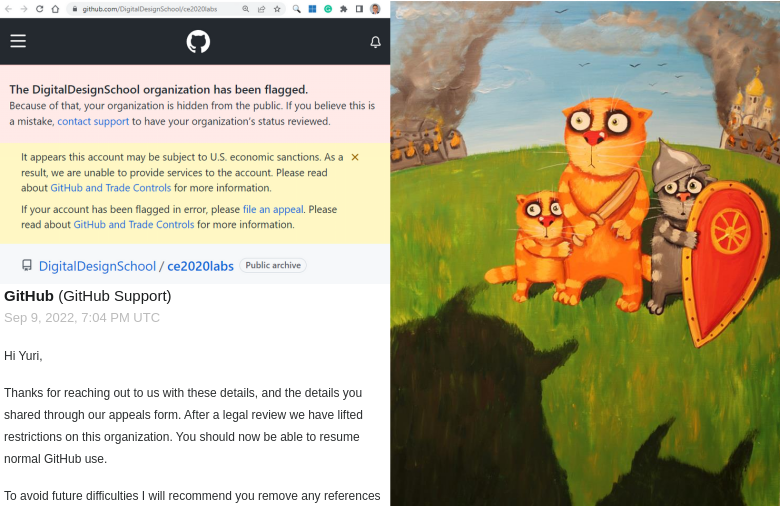

В прошлое воскресенье 4 сентября я обнаружил, что GitHub-организация DigitalDesignSchool, в которой я являюсь одним из владельцев, забанена Гитхабом с формулировкой "ваш аккаунт может быть предметом американских экономических санкций".

Пораскинув мозгами и посовещавшись с моим приятелем, основателем московского интернет-провайтера RiNet Сергеем Рыжковым, у которого в тот же день забанили счет в Ситибанке в Лондоне, я решил: нужно бороться.