В России не любят Линукс. Студенты и корпорации всячески отлынивают его использовать, даже если Линукс насаждают преподаватели или госзаказчики. Но есть область, в которой Линукс придется полюбить. Это разработка микросхем. Даже внутри Apple и Microsoft инженеры используют Synopsys Design Compiler / IC Compiler и Cadence Genus / Innovus, у которых вообще нет версий для Windows и MacOS, только для Linux. Да, я знаю, что Synopsys и Cadence ушли из России. Но даже открытые тулы для синтеза ASIC - Open Lane - есть только под Linux.

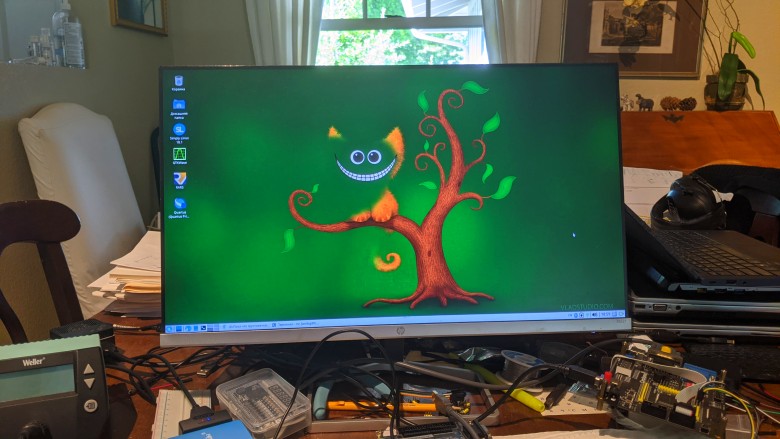

Я уже несколько лет использую для семинаров по FPGA загружаемые через USB SSD диски, на который ставится весь необходимый софтвер. Такое решение позволяет избежать агонии первого дня семинара, когда приходит куча народу со своими ноутбуками, три часа ставят Quartus, а потом мучаются с драйверами USB Blaster для китайского контрафактного клона, который без танцев с бубном не хотят поддерживать не Win10, ни Linux, ни особенно Win11, который хочет подписанные драйверы.

А как же виртуальные машины? - спросите вы. С моей точки зрения они вносят дополнительный уровень танцев с бубном. И это не мое дремучее мнение - так же считает мой приятель, который работал над виртуализацией в Микрософте. То оно USB порт не пробивает, то еще какие-нибудь глюки. Плюс учить дополнительные опции, качать и копировать файлы в десятки гигабайт. А тут вставил в USB порт, и если загрузится, то заработает.

Конечно, загружаемые SSD тоже не без проблем: тут и Legacy BIOS boot против UEFI boot, и Secure Boot с Bit Locker, и зловещий "хвост GPT", и отрубание всего из-за скачка напряжения в USB хабе - но с этими проблемами мы методично разобрались. Решение я и описываю в этой заметке, предназначенной в первую очередь для учеников и руководителей кластеров в Школе Синтеза Цифровых Схем, которая начинается с сентября в 14 российских городах (объявления и точных дат еще нет, но уже записалось 200 учеников).

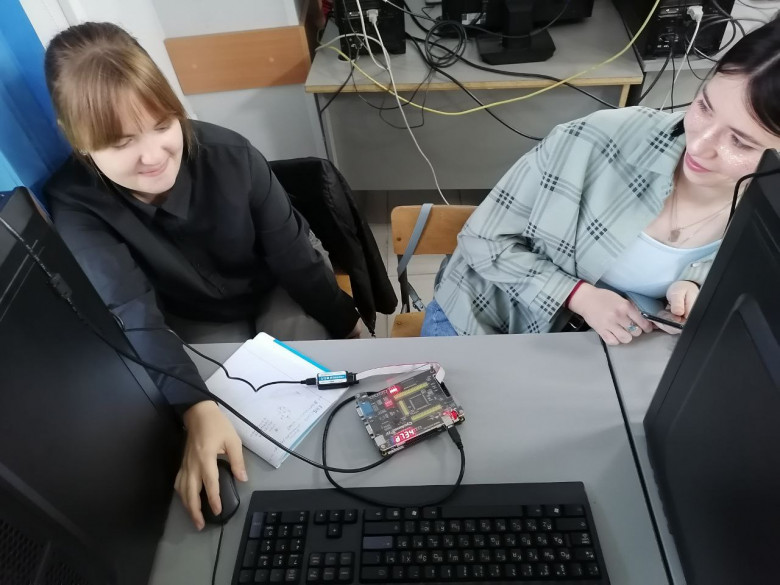

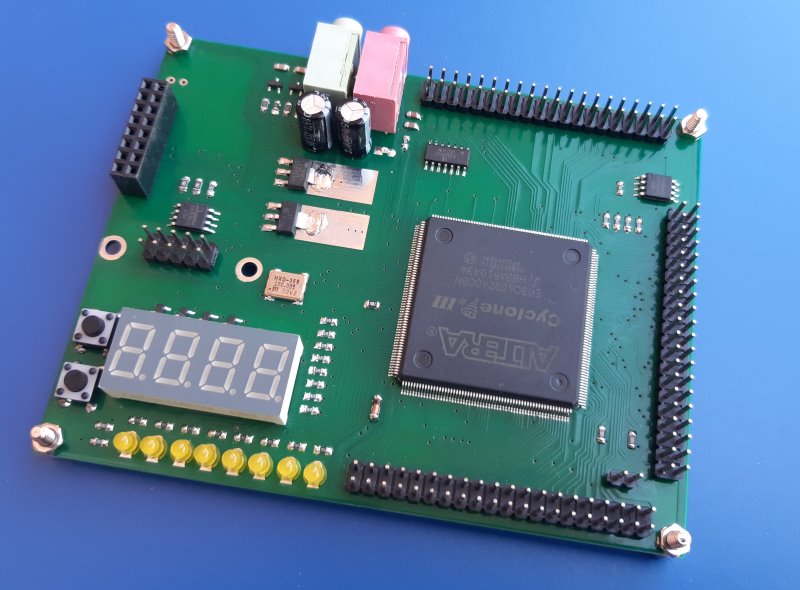

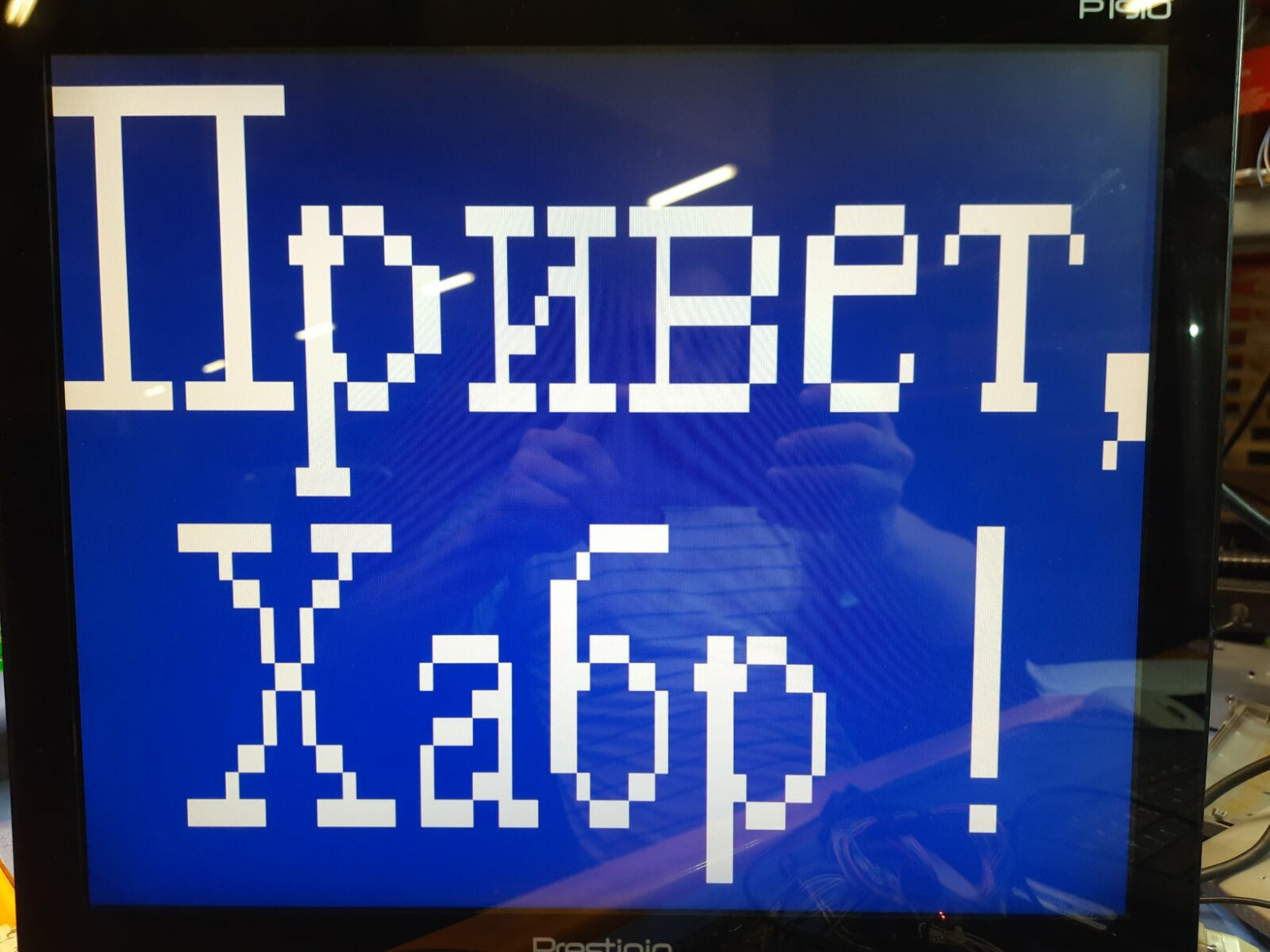

Прежде всего: как выглядит загружаемый SSD? А вот так: