Комментарии 20

Да, тех процесс с якобы 5нм уменьшился до якобы 3нм, а плотность транзисторов стала больше всего в 1.1-1.7 раза. Интересно, что маркетологи придумают еще, когда освоят «1нм» техпроцесс маркетинг?

-3

А какой физический пределе для производства чипов когда сказываются квантовые эффекты? Сколько это нм? Гугление ничего вразумительного не дает.

+1

пусть называют свои нанометры как хотят конечно, но тогда плотность транзисторов пусть тоже указывают. А то смысл пытаться сравнивать техпроцесс у них и конкурента, если там «плотность увеличена в 1.1-1.7 раз», учитывая что сравниваются вообще техпроцессы 3нм и 5нм, а не 2нм из сабжа

0

а он и не сильно уменьшился:

0

Площадь ячейки SRAM у техпроцессов TSMC:

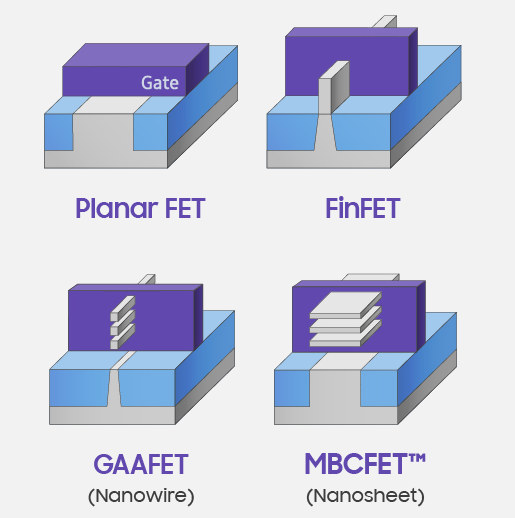

20nm — 0,081 µm² (Planar)

5nm — 0,021 µm² (FinFET)

3nm — ~0,0152 µm² (ориентировочно; GAAFET?)

20nm — 0,081 µm² (Planar)

5nm — 0,021 µm² (FinFET)

3nm — ~0,0152 µm² (ориентировочно; GAAFET?)

0

40-28nm — это УЖЕ FinFET — там он постепенно появлялся.

в чистом виде Planar — до 60nm

по размерностям ячейки — прогрессия заметная, но связана она скорее с размерностями «разделяющих зон», а не размерностями элементов — тк реально:

и так уже много лет размерность транзистора почти не меняется вроде из-за проявления квантовых эффектов она вроде не может быть меньше 20нм — гуглим тема Большая и интересная, по этому транзисторы стали более трехмерными что бы сохраняя размерности увеличить плотность.

в чистом виде Planar — до 60nm

по размерностям ячейки — прогрессия заметная, но связана она скорее с размерностями «разделяющих зон», а не размерностями элементов — тк реально:

и так уже много лет размерность транзистора почти не меняется вроде из-за проявления квантовых эффектов она вроде не может быть меньше 20нм — гуглим тема Большая и интересная, по этому транзисторы стали более трехмерными что бы сохраняя размерности увеличить плотность.

0

Nordicx86

(не туда ответил)

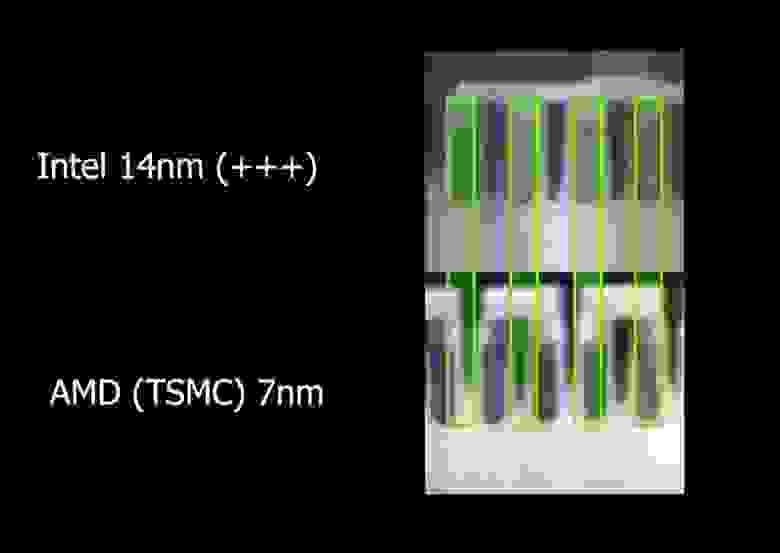

На первой картинке процесс TSMC HP с плотностью 66МТр/ммкв против Intel 37МТр/ммкв (сколько добавляют +++ я не знаю).

По одной размерности, показанной на фотке, у TSMC влезает на 25% больше транзисторов.

HD библиотеки позволяют паковать 96МТр/ммкв, т.е. вдвое больше чем у Интел.

Т.е. проще говоря, площадь транзистора уменьшилась. ЧТД.

(не туда ответил)

На первой картинке процесс TSMC HP с плотностью 66МТр/ммкв против Intel 37МТр/ммкв (сколько добавляют +++ я не знаю).

По одной размерности, показанной на фотке, у TSMC влезает на 25% больше транзисторов.

HD библиотеки позволяют паковать 96МТр/ммкв, т.е. вдвое больше чем у Интел.

по этому транзисторы стали более трехмерными что бы сохраняя размерности увеличить плотность.

Т.е. проще говоря, площадь транзистора уменьшилась. ЧТД.

0

Тут говорить о площади не совсем уместно — тк детали всё таки трехмерные… да и

физические размерности транзисторов еще на 28нм уперлись в предел — дальше начинаются «квантовые» эффекты — всё что «тоньше» это уже ухищрения по оптимизации размещения и повышению точности ТП…

Новые вариации транзисторов по размерности не меньше старых, но из-за более оптимальной структуры и качества ТП сократились токи утечки и размерности «грязных» зон вокруг транзистора что позволило упаковать их чуть больше на туже площадь…

В целом начиная с 28нм борются сейчас в основном за оптимизацию размещения и утечки — тк в остальном «усё почти предел» и дальнейшие не революционные оптимизации уже требуют запредельных затрат.

у IBM была отличная видяшка — с 3D моделями разных транзисторов в одном масштабе — там было отлично видно соотношения между размерностями транзисторов разных ТП и было четко видно что они не сильно отличаются…

физические размерности транзисторов еще на 28нм уперлись в предел — дальше начинаются «квантовые» эффекты — всё что «тоньше» это уже ухищрения по оптимизации размещения и повышению точности ТП…

Новые вариации транзисторов по размерности не меньше старых, но из-за более оптимальной структуры и качества ТП сократились токи утечки и размерности «грязных» зон вокруг транзистора что позволило упаковать их чуть больше на туже площадь…

В целом начиная с 28нм борются сейчас в основном за оптимизацию размещения и утечки — тк в остальном «усё почти предел» и дальнейшие не революционные оптимизации уже требуют запредельных затрат.

у IBM была отличная видяшка — с 3D моделями разных транзисторов в одном масштабе — там было отлично видно соотношения между размерностями транзисторов разных ТП и было четко видно что они не сильно отличаются…

0

Тут говорить о площади не совсем уместно — тк детали всё таки трехмерные

И что с того? Процессоры плоские.

Лишь площадь определяет сколько таких чипов выходит с пластины.

Жильцов в небоскрёб влезает гораздо больше чем в одноэтажный дом аналогичной площади.

Размер по вертикали актуален только для 3D NAND.

0

И что с того? Процессоры плоские.

Лишь площадь определяет сколько таких чипов выходит с пластины.

уже давно не совсем плоские… AMD вовсю 2,5D камнями торгует…

Полностью трехмерные кристаллы пока что только появляются но я так думаю мы их увидим еще до 2025 — Xilinx например выпускает многослойные FPGA с 2016 если не раньше.

0

уже давно не совсем плоские… AMD вовсю 2,5D камнями торгует…

Плоские.

Стекинг не отменяет того, что на кристалле процессора лишь один слой транзисторов.

Высота планарного транзистора от finfet отличается на десяток нм, т.е. не играет вообще никакой роли, даже если вы бутерброд из сотен кристаллов делаете.

Если разница составляет 10нм, то 100 слоёв finfet от планарного отличаются на 0,001мм.

В общем вот вам калькулятор выхода годных с пластины.

Постарайтесь там найти третье измерение.

caly-technologies.com/die-yield-calculator

Полностью трехмерные кристаллы пока что только появляются

Я уже писал про 3D NAND, которую нынче в 128 слоёв делают. Только она не процессор.

0

Высота планарного транзистора от finfet отличается на десяток нм, т.е. не играет вообще никакой роли, даже если вы бутерброд из сотен кристаллов делаете.

Я уже писал про 3D NAND, которую нынче в 128 слоёв делают. Только она не процессор.

Реально — сейчас 3D чипов нет разве что только в лабах и прототипах всё что сейчас есть это 2,5D типа многослойных кристаллов или напайки одного кристалла на другой.

Xilinx просто «Клеит» один чип на другой — это 2.5D при этом они умудряются Жить с TDP под 250 Ватт на 16нм — так что почему не внедрят эту технологию в Процессоры пока не понятно но скорее всего из-за сложности и стоимости.

Насколько я знаю сейчас 3D чипы пытаются сделать в РФ и в Франции — в РФ еще пытаются воскресить идею «нано ламп» с терагерцевыми диапазонами рабочих частот… это кстати то же будет 3D чип из-за структуры и строения ламп.

0

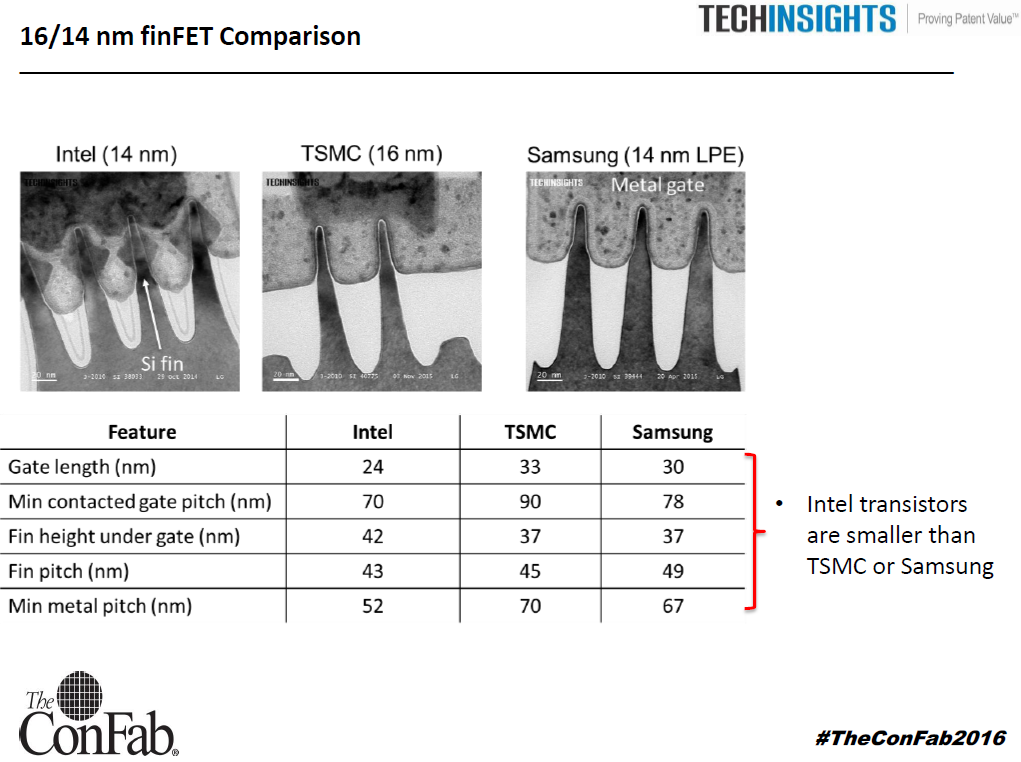

Что эта картинка должна символизировать?

Транзисторы там показаны в разном масштабе.

Я говорю о разнице планарного и finfet транзистора на сравнимом техпроцессе.

Несомненно, нефтяная плёнка на поверхности океана имеет какую-то толщину, но вы пытаетесь сделать вид как будто она что-то кардинально меняет.

Как ваши успехи с поиском третьего измерения на схеме пластины, кстати?

Могу и в третий раз написать — 3D NAND.

habr.com/ru/company/ocz/blog/391899

Транзисторы там показаны в разном масштабе.

Я говорю о разнице планарного и finfet транзистора на сравнимом техпроцессе.

Несомненно, нефтяная плёнка на поверхности океана имеет какую-то толщину, но вы пытаетесь сделать вид как будто она что-то кардинально меняет.

Как ваши успехи с поиском третьего измерения на схеме пластины, кстати?

Реально — сейчас 3D чипов нет

Могу и в третий раз написать — 3D NAND.

habr.com/ru/company/ocz/blog/391899

0

что идет за 1нм?

0

Зарегистрируйтесь на Хабре, чтобы оставить комментарий

TSMC запускает 2-нм линию производства чипов и продвигается к 1-нм рубежу