Comments 23

Хорошее дело. А FPGA сама идентификатор не проверяет при старте?

И небольшой коммент: после создания системы в QSys лучше добавлять в проект не .qsys, а .qip (лежит в .\qsys_system\synthesis\qsys_system.qip). Первый вызывает полную перегенерацию qsys-подсистемы при перекомпиляции, а второй подключает уже имеющиеся результаты генерации системы.

И небольшой коммент: после создания системы в QSys лучше добавлять в проект не .qsys, а .qip (лежит в .\qsys_system\synthesis\qsys_system.qip). Первый вызывает полную перегенерацию qsys-подсистемы при перекомпиляции, а второй подключает уже имеющиеся результаты генерации системы.

+3

Скорее всего, не проверяет, что логично, ведь в целом — нет жёсткого требования, какой ёмкости конфигуратор использовать для конкретного кристалла. Главное — чтобы этой ёмкости хватило. По крайней мере, всё работает именно с 32-й флэшкой, а EPCS — бывает 16, бывает 64 и далее — уже вверх. А 32 — не бывает. И всё работает. Проверено.

За комментарий по подключаемым файлам — спасибо. Век живи — век учись. Буду пробовать.

За комментарий по подключаемым файлам — спасибо. Век живи — век учись. Буду пробовать.

0

Раз флэшки сами по себе совместимы и только альтеровскому программатору не нравится прочитанный ID (что есть свинство со стороны альтеры, можно же было сделать предупреждение «ID не совпали, продолжить на свой страх и риск?», но ведь кто тогда будет покупать их флэш втридорога), то тогда можно со спокойной совестью взять в руки ollydbg и просто объяснить программатору, что не надо ругаться на несовпадение ID, а лишь выполнить пару nopов вместо перехода на обработку ошибки и продолжить работать как ни в чём ни бывало.

+1

Тоже вариант. Но, в целом, как видим, можно воспользоваться и фирменными Альтеровскими вещами, которые всё равно установились, просто их надо несколько извратно вызывать.

Но на самом деле, готовим прошивальщик — один раз на жизнь схемы и ей подобных схем.

Готовим файл под прошивку — единожды на версию, так как всё равно при отладке он льётся прямо в ПЛИС, на то она и отладка. Причём готовить — что этим способом, что мышкой давить — и там и тут надо кучку действий выполнить.

Ну, и дальше — только кто платы прошивает, должен будет ввести заклинание один раз за смену против трёх движений мышкой. Потом — просто «Вверх, Enter» нажимать.

Не так и сложно, как оказалось.

Но на самом деле, готовим прошивальщик — один раз на жизнь схемы и ей подобных схем.

Готовим файл под прошивку — единожды на версию, так как всё равно при отладке он льётся прямо в ПЛИС, на то она и отладка. Причём готовить — что этим способом, что мышкой давить — и там и тут надо кучку действий выполнить.

Ну, и дальше — только кто платы прошивает, должен будет ввести заклинание один раз за смену против трёх движений мышкой. Потом — просто «Вверх, Enter» нажимать.

Не так и сложно, как оказалось.

0

Кстати, на самом деле, они все совместимы на чтение. Задали адрес, дальше — нам идут данные, а адрес — автоинкрементируется. А вот на запись — у них действительно могут быть всякие несовместимости по размеру страницы и прочему. Не даром же приходится заполнять конфигурационный файл. Почему нельзя его заполнять для штатного GUI-программатора — вопрос открытый.

0

Например, по идентификатору оно может подгружать sector map. К тому же патчить компиляторы и прошивальщики — занятие сомнительное, и на практике порождает неуловимые баги.

0

Естественно, простой патч будет работать при условии что различие только в ID.

habrahabr.ru/post/110395

habrahabr.ru/post/302570

а тут всего лишь размер сектора поправить если вдруг не совпадёт :)

habrahabr.ru/post/110395

habrahabr.ru/post/302570

а тут всего лишь размер сектора поправить если вдруг не совпадёт :)

0

Если вы предлагаете заменить одни значения другими — то это действительно не должно повлечь последствий, однако тогда функционал больше не станет, в то время как в статье описано как не потеряв старый добиться нового (пусть и таким путем).

А серьезная модификация утилиты с изменением размеров внутренних таблиц может плохо кончится. Мне встречался компилятор, который во внутренней логике использовал собственную хеш-сумму (кажется, простым однобайтовое сложение), и при этом всегда выдавал валидный, но каждый раз работающий по разному бинарник.

К тому же, логика движка игры, как правило, не очень сложная. А логика компиляторов, синтезаторов и прошивальщиков на порядок сложнее, и цена ошибки на порядок выше.

А серьезная модификация утилиты с изменением размеров внутренних таблиц может плохо кончится. Мне встречался компилятор, который во внутренней логике использовал собственную хеш-сумму (кажется, простым однобайтовое сложение), и при этом всегда выдавал валидный, но каждый раз работающий по разному бинарник.

К тому же, логика движка игры, как правило, не очень сложная. А логика компиляторов, синтезаторов и прошивальщиков на порядок сложнее, и цена ошибки на порядок выше.

0

Ну никакого нового функционала нет, только прошивка неродной конфигурационной памяти, штатным бластером.

Протокол общения с бластером впринципе известен, BSDL файлы для цыклона есть, команды для для работы с флешью — в её даташите, то есть если уж изобретать велосипеды, можно было и самому программатор соорудить который будет шить данный «нестандартный» флэш через усббластер как напрямую(такой велосипед я и сам делал, хотя и готовых наверняка хватает), так и через дрыгание ногами подопытной плис через jtag, что даже дополнительного коннектора к памяти не потребует.

Беглый осмотр даташитов M25P32 и EPCS показал что размеры секторов(65К) и страниц(256) абсолютно одинаковые, соответственно единственное различие, которое и не нравится программатору это прочитанный ID, что очень легко вылечить, убедив его, что он всегда читает правильный ID, не влезая при этом в сам процесс программирования и ничего там не модифицируя.

А вообще подход описанный автором конечно правильный. Ещё более правильный путь это, пожалуй, иметь возможность обновления флэша в самой боевой прошивке, и просто загружать её через jtag, а затем «обновляться» штатными средствами, но такой отдельный небольшой велосипедик тут тоже подходит.

Протокол общения с бластером впринципе известен, BSDL файлы для цыклона есть, команды для для работы с флешью — в её даташите, то есть если уж изобретать велосипеды, можно было и самому программатор соорудить который будет шить данный «нестандартный» флэш через усббластер как напрямую(такой велосипед я и сам делал, хотя и готовых наверняка хватает), так и через дрыгание ногами подопытной плис через jtag, что даже дополнительного коннектора к памяти не потребует.

Беглый осмотр даташитов M25P32 и EPCS показал что размеры секторов(65К) и страниц(256) абсолютно одинаковые, соответственно единственное различие, которое и не нравится программатору это прочитанный ID, что очень легко вылечить, убедив его, что он всегда читает правильный ID, не влезая при этом в сам процесс программирования и ничего там не модифицируя.

А вообще подход описанный автором конечно правильный. Ещё более правильный путь это, пожалуй, иметь возможность обновления флэша в самой боевой прошивке, и просто загружать её через jtag, а затем «обновляться» штатными средствами, но такой отдельный небольшой велосипедик тут тоже подходит.

0

У Квартуса при преобразовании файлов для заливки во флешку есть вкладка «Advanced», и там есть галочка — «Disable EPCS ID check». Менял на своей DE0 флешку на бОльшую 25-ую, в Q12.1 опция сработала без проблем.

+1

"Когда в руках молоток, всё вокруг кажется гвоздями."

Как-то очень давно при первом знакомстве с квартусом тоже не смог сходу найти галочку которая разрешает рядом располагать обычные кмоп выходы и лвдс (там надо было просто частоту переключения в 0 выставить, иначе ругается что будут наводки с кмопа на лвдс), вылечил дебагером :)

0

Из любого описания на FPGA известно, что для хранения их конфигураций используются специальные микросхемы – конфигураторы.

автор видимо не знаком с FPGA со встроенным флешем

0

Ой знаком. Наши Заказчики с целью защиты от клонирования в своей плате такую использовали однажды… Вернее, они использовали с однократкой без возможности перешивки. Воспоминания — только самые ужасные.

Так или иначе, спасибо за замечание, добавил одно слово в текст. Теперь там говорится про описания на популярные FPGA.

Так или иначе, спасибо за замечание, добавил одно слово в текст. Теперь там говорится про описания на популярные FPGA.

0

Пожалуйста, но из описания на популярные Lattice FPGA известно, что дополнительные микросхемы конфигураторы не нужны, так как для этого есть встроенная флеш память.

0

Посмотрел статистику продаж их и средств разработки на них и на Altera/Xilinx на Ali Express. Посмотрел предложения в отечественных конторах. Давайте сойдёмся на том, что они ещё не настолько популярны, как их загружаемые конкуренты. А статья — вообще про Альтеру. Которая на сегодняшний день в паре с Xilinx пока, вроде, популярней остальных. Усложнять фразу в основном тексте в сегодняшних реалиях — не вижу смысла. Особенно если учитывать, что дальше — даже Xilinx не рассматривается.

0

Вынес свои мысли в виде предложения в основной текст.

0

встроенный флэш там у мелких ICE и MachXO.

те что побольше, ECP, загружаются снаружи.

те что побольше, ECP, загружаются снаружи.

0

Кстати, по поводу назначения пинов для флешки — в моём случае не получается вообще никак, они заблокированы как «Dedicated Programming». Можно ли это обойти вообще?

0

К сожалению, сильно больше, чем показано в видео, рассуждать не могу. Я всегда опытным путём под конкретный случай пытаюсь подогнать, так что теоретизировать об общих вещах, без предварительных изучений конкретного случая — сложно.

Как показано в видео — точно работает. Там есть, как войти в настройку поведения этих ножек, на что переключить, кратко видно, какие ещё варианты имеются в списках. В тексте это сложно разъяснить, именно поэтому я считаю, что первично всё-таки видео (но без текста нельзя делать публикации, поэтому он тоже нужен). Возможно, из того, что там ещё попало в кадр, можно какие-то идеи вывести под те чипы, что у Вас (для четвёртого Циклона — просто следовать этой инструкции).

А дальше — если не получается какая-то конкретика, то нужно уже под конкретный случай занудно документацию смотреть, «что там можно, что нельзя».

Как показано в видео — точно работает. Там есть, как войти в настройку поведения этих ножек, на что переключить, кратко видно, какие ещё варианты имеются в списках. В тексте это сложно разъяснить, именно поэтому я считаю, что первично всё-таки видео (но без текста нельзя делать публикации, поэтому он тоже нужен). Возможно, из того, что там ещё попало в кадр, можно какие-то идеи вывести под те чипы, что у Вас (для четвёртого Циклона — просто следовать этой инструкции).

А дальше — если не получается какая-то конкретика, то нужно уже под конкретный случай занудно документацию смотреть, «что там можно, что нельзя».

0

В том-то и дело, что эти ноги недоступны для переключения.

У меня — 5-ый циклон, SoC. В настройках ног только это:

Я уже вручную в qsf-файле прописал эти ноги — ругается при сборке.

У меня — 5-ый циклон, SoC. В настройках ног только это:

Я уже вручную в qsf-файле прописал эти ноги — ругается при сборке.

0

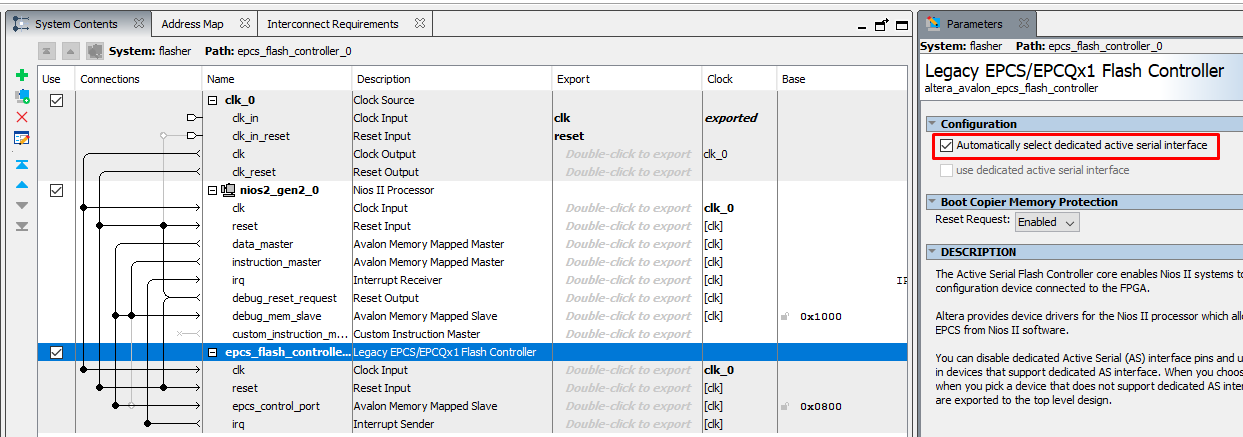

Всё, проблему решил.

В Qsys не надо было настраивать выходы программатора как EXTERNAL — оно автоматом подхватывает дефолтные ноги само, без лишних телодвижений:

В итоге флешку увидело, прочитало и прошило.

В Qsys не надо было настраивать выходы программатора как EXTERNAL — оно автоматом подхватывает дефолтные ноги само, без лишних телодвижений:

В итоге флешку увидело, прочитало и прошило.

0

Век живи — век учись. Спасибо, что описали. Если возникнет подобное — будет уже готовое решение (с пятым SoC я пока не подружился, хотя уже несколько подходов сделал — пытаюсь понять, как там Bare Metal приложения делаются, но слишком много информации сразу — не хватает свободного времени, чтобы переварить).

0

Sign up to leave a comment.

Использование произвольных DataFlash 25-й серии вместо дорогих конфигураторов FPGA Altera без дополнительной аппаратуры