Comments 9

Справедливости ради отмечу, что у коллектива, в котором работает Плеханов Л.П. довольно много наработок по части самосинхронной схемотехники. Более 20 патентов по самосинхронике, включая международные патенты (США).

ipiran.ru/products/patents/patents

Также решения являются не только теоретическими, но и практическими. Например, буквально недавно вышла книга «Библиотека функциональных ячеек для проектирования самосинхронных полузаказных микросхем серий 5503 и 5507»

www.ozon.ru/context/detail/id/141734409

САПР «Ковчег» насколько я понимаю позволяет проектировать самосинхронные схемы в базисе БМК серий 5504 и 5507.

Кроме того, уже выполнен по технологии 65 нм самосинхронный делитель и блок FMA для процессора КОМДИВ-64.

П.С.: Автору книги Ваш пост я переправил :)

ipiran.ru/products/patents/patents

Также решения являются не только теоретическими, но и практическими. Например, буквально недавно вышла книга «Библиотека функциональных ячеек для проектирования самосинхронных полузаказных микросхем серий 5503 и 5507»

www.ozon.ru/context/detail/id/141734409

САПР «Ковчег» насколько я понимаю позволяет проектировать самосинхронные схемы в базисе БМК серий 5504 и 5507.

Кроме того, уже выполнен по технологии 65 нм самосинхронный делитель и блок FMA для процессора КОМДИВ-64.

П.С.: Автору книги Ваш пост я переправил :)

+2

Да, я могу гордиться своим дядей.

0

Забыл упомянуть еще одну деталь. В книге достаточное внимание уделено проблеме длинных проводов, то есть проводов, выходящих за пределы эквихронных зон. Предлагаемое решение находится на физическом уровне. Но проблему можно решить на логическом уровне, причем кардинально. Надежность схемы зависит исключительно от соотношений задержек, примеры которых представлены в статье. Очевидное решение: локализовать задержки всех длинных проводов в правых частях неравенств.

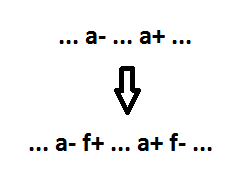

Если принять, что схема состоит из подсхем, а каждая подсхема располагается целиком в эквихронной зоне, то длинные провода это провода входных сигналов подсхем. Отсюда вывод: входные сигналы подсхем нельзя использовать в качестве подхватывающих для какого-либо перехвата. Достигается это не сложной коррекцией (a — входной сигнал, f — дополнительный сигнал):

Все сигналы, переключения которых являются следствиями переключений сигнала a, теперь имеют реализацию (f=NOT(a)). В дальнейшем сигнал a при синтезе подсхемы можно не рассматривать. Сигнал a в перехватах не участвует. Задержка длинного провода в левую часть неравенства попасть теперь не может. Задержка длинного провода может попасть только в правую часть неравенства, как транзитная задержка (если переключение сигнала a располагается между двумя событиями, определяющими перехват).

Парадоксальным образом теперь длинный провод играет на повышение надежности схемы. Это решение аналог решения, приведенного в книге, но не на физическом, а на логическом уровне. Ну и не надо забывать, что взаимодействие между подсхемами должно быть организовано по принципу запрос-ответ.

Если принять, что схема состоит из подсхем, а каждая подсхема располагается целиком в эквихронной зоне, то длинные провода это провода входных сигналов подсхем. Отсюда вывод: входные сигналы подсхем нельзя использовать в качестве подхватывающих для какого-либо перехвата. Достигается это не сложной коррекцией (a — входной сигнал, f — дополнительный сигнал):

Все сигналы, переключения которых являются следствиями переключений сигнала a, теперь имеют реализацию (f=NOT(a)). В дальнейшем сигнал a при синтезе подсхемы можно не рассматривать. Сигнал a в перехватах не участвует. Задержка длинного провода в левую часть неравенства попасть теперь не может. Задержка длинного провода может попасть только в правую часть неравенства, как транзитная задержка (если переключение сигнала a располагается между двумя событиями, определяющими перехват).

Парадоксальным образом теперь длинный провод играет на повышение надежности схемы. Это решение аналог решения, приведенного в книге, но не на физическом, а на логическом уровне. Ну и не надо забывать, что взаимодействие между подсхемами должно быть организовано по принципу запрос-ответ.

0

Сергей, книга, о которой Вы пишете, не несет ни теории (ее там нет вообще), ни практической пользы — таких лог. элементов как в этой книге ни в одном суб 100нм логическом базисе не найдешь. Читайте лучше первоисточник Моделирование параллельных процессов.

+1

ЛОЛ. А с каких пор технологический базис стал влиять на схемотехнику? Самосинхронные схемы уже проектировались в частности в ИПИ РАН в базисе 65 нм, и для того же Кэденса были реализованы IP ядра, просто они в библиотеку не включены, потому что Кэденс денег за это просит, а оно как бы при текущей раскрученности самосинхронных схем смысла не несет.

0

Коллега, не мне Вас учить, пусть за Вас краснеют Ваши учителя. Написали полнейшую ересь. 1. Базис элементов влияет на схемотехнику напрямую, и особенно в СС. 2. Какой такой Кэденс? Кэденс, это производитель тулов, один из. Библиотеки элементов же предоставляет фабрика, и в некоторых случаях — дезайн хаусы. Т.е. Кэденс никак не может просить денег за включение IP в библиотеку, Вы что то с чем то спутали.

Элемент, на который я кивал, приведен выше — это 8-ми входовой элемент. Такие элементы делать можно, но чтобы они эффективно работали, нужно напряжение питания около 3 вольт (оценочно — Vth * число входов). На процессах суб 100нм питание элементов ядра от 1.2В и ниже — до 700мВ. Питание можно поднять, но очень незначительно, поскольку на тонких процессах возможен пробой диэлектрика (физики — поправьте, если соврал), и фабрика не гарантирует исправность приборов. Итого, 8-ми входовой элемент при недостатке питания делать нет смысла, если только он не составной. А составные элементы не подходят для СС. Варшавский этого знать не мог, в его время тонких процессов не было. А вот зачем такие схемы публиковать сейчас — вопрос.

Элемент, на который я кивал, приведен выше — это 8-ми входовой элемент. Такие элементы делать можно, но чтобы они эффективно работали, нужно напряжение питания около 3 вольт (оценочно — Vth * число входов). На процессах суб 100нм питание элементов ядра от 1.2В и ниже — до 700мВ. Питание можно поднять, но очень незначительно, поскольку на тонких процессах возможен пробой диэлектрика (физики — поправьте, если соврал), и фабрика не гарантирует исправность приборов. Итого, 8-ми входовой элемент при недостатке питания делать нет смысла, если только он не составной. А составные элементы не подходят для СС. Варшавский этого знать не мог, в его время тонких процессов не было. А вот зачем такие схемы публиковать сейчас — вопрос.

+1

Интересно, и чем отличается базис синхронной схемотехники от самосинхронной? И как же так вдруг в ИПИ РАН проектируют схемы под 65 нм, если вы утверждаете, что это невозможно?

Вы правда думаете, что все вручную разводят? Изначально конечно вручную, но свою библиотеку элементов уже создали, только вот Кэденс за просто так частные библиотеки не берет, если вы не в курсе.

Вы правда думаете, что все вручную разводят? Изначально конечно вручную, но свою библиотеку элементов уже создали, только вот Кэденс за просто так частные библиотеки не берет, если вы не в курсе.

0

я, конечно, не Сергей, но почитаю.

0

Почитаю.

0

Sign up to leave a comment.

Мои замечания о книге Л.П. Плеханова «Основы самосинхронных электронных схем»