Синхронизация является основным методом борьбы с состязаниями сигналов в цифровых схемах.

В отличие от обычных асинхронных триггеров, где в соответствии с таблицей истинности переключение происходит в те моменты времени, когда меняются сигналы на информационных входах, синхронизирующие (тактируемые) триггеры имеют еще и управляющий вход (обычно на схемах обозначают как вход C). Если сигнал на этом входе принимает разрешающее значение, то триггер работает как асинхронный. Если сигнал на тактирующем входе имеет запрещающее значение, то триггер не реагирует на изменение сигналов на информационных входах и сохраняет ту информацию, которую он записал при последнем разрешении на запись.

Синхронизация бывает нескольких типов:

В этой статье ограничимся рассмотрением первого случая.

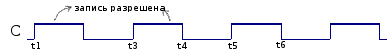

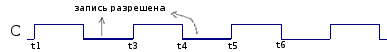

При сигнале C = “1” (в моментах от t2n-1 до t2n) запись разрешена, при C = “0” — режим хранение.

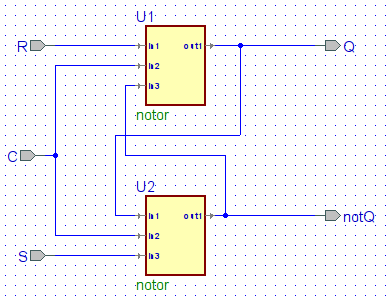

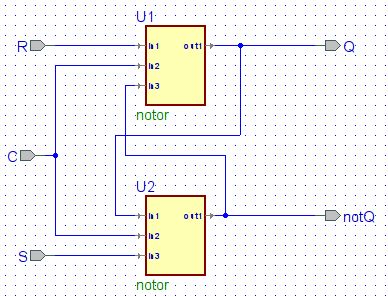

Проиллюстрируем это на RS триггере со синхронизацией на базе элементов “или-не” (U1, U2) с тремя входами.

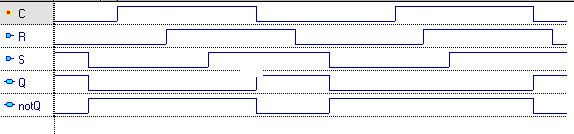

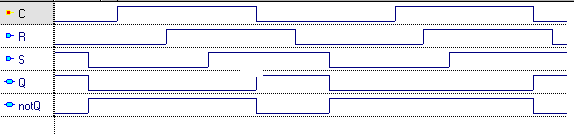

Временная диаграмма работы данного триггера (без считывания задержки на вентилях):

В логических элементах “или-не” доминирующим сигналом является “1”, поэтому при сигнале C = 1, сигналы на входах R и S блокируются и триггер будет находиться в режиме хранения. При C = 0 схема работает как обычный RS триггер.

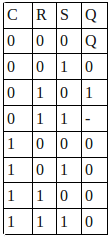

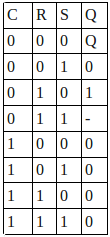

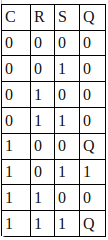

Таблица истинности данной схемы:

При сигнале C = “0” (в моментах от t2n до t2n+1) запись разрешена, при C = “1” — режим хранение.

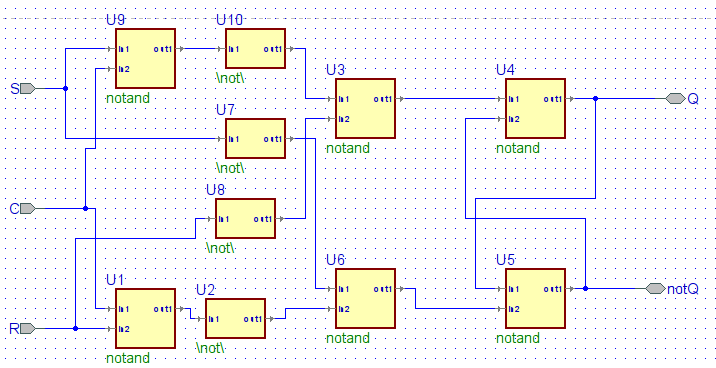

Представим работу тактируемого триггера на основе синхронизирующего E триггера на базе логических элементов “и-не” (U9, U3, U4, U1, U6, U5) и “не” (U10, U7, U8, U2).

На схеме логические элементы “и-не” U9, U3 и инвертор U10 образовывают обычный логический элемент “и-не” с тремя входами. Аналогично для U1, U2, U6.

Временная диаграмма работы схемы:

Так как в элементах “и-не” доминирующим сигналом является “0”, то поступающие сигналы C = 0 блокируют R и S сигналы и поэтому триггер будет сохранять свое исходное состояние.

При C = 1, поступление сигналов с входов R и S будет разрешено и схема будет работать как обычный S триггер (переключается в единичное состояние):

Сигналы C, S и notR поступают к входам U3, а C, notS и R поступают к входам U6. Получаем на входах RS триггера (U4+U5) сигналы (not S || R) и (S || not R).

Таблица истинности данной схемы:

У триггеров с синхронизацией по уровню сигнала есть один недостаток — изменение входных сигналов и ихнее возвращение в исходное положение может происходить во время разрешения тактирующим сигналом, что приведет к тому, что выход схемы насквозь просматривает вход в течении некоторого интервала времени.

В отличие от обычных асинхронных триггеров, где в соответствии с таблицей истинности переключение происходит в те моменты времени, когда меняются сигналы на информационных входах, синхронизирующие (тактируемые) триггеры имеют еще и управляющий вход (обычно на схемах обозначают как вход C). Если сигнал на этом входе принимает разрешающее значение, то триггер работает как асинхронный. Если сигнал на тактирующем входе имеет запрещающее значение, то триггер не реагирует на изменение сигналов на информационных входах и сохраняет ту информацию, которую он записал при последнем разрешении на запись.

Синхронизация бывает нескольких типов:

- По уровню синхронизирующего сигнала

- По уровню сигнала “1”

- По уровню сигнала “0”

- По фронту

- По заднему фронту

- По переднему фронту

В этой статье ограничимся рассмотрением первого случая.

Синхронизация по уровню сигнала “1”

При сигнале C = “1” (в моментах от t2n-1 до t2n) запись разрешена, при C = “0” — режим хранение.

Проиллюстрируем это на RS триггере со синхронизацией на базе элементов “или-не” (U1, U2) с тремя входами.

Временная диаграмма работы данного триггера (без считывания задержки на вентилях):

В логических элементах “или-не” доминирующим сигналом является “1”, поэтому при сигнале C = 1, сигналы на входах R и S блокируются и триггер будет находиться в режиме хранения. При C = 0 схема работает как обычный RS триггер.

Таблица истинности данной схемы:

Синхронизация по уровню сигнала “0”

При сигнале C = “0” (в моментах от t2n до t2n+1) запись разрешена, при C = “1” — режим хранение.

Представим работу тактируемого триггера на основе синхронизирующего E триггера на базе логических элементов “и-не” (U9, U3, U4, U1, U6, U5) и “не” (U10, U7, U8, U2).

На схеме логические элементы “и-не” U9, U3 и инвертор U10 образовывают обычный логический элемент “и-не” с тремя входами. Аналогично для U1, U2, U6.

Временная диаграмма работы схемы:

Так как в элементах “и-не” доминирующим сигналом является “0”, то поступающие сигналы C = 0 блокируют R и S сигналы и поэтому триггер будет сохранять свое исходное состояние.

При C = 1, поступление сигналов с входов R и S будет разрешено и схема будет работать как обычный S триггер (переключается в единичное состояние):

Сигналы C, S и notR поступают к входам U3, а C, notS и R поступают к входам U6. Получаем на входах RS триггера (U4+U5) сигналы (not S || R) и (S || not R).

Таблица истинности данной схемы:

У триггеров с синхронизацией по уровню сигнала есть один недостаток — изменение входных сигналов и ихнее возвращение в исходное положение может происходить во время разрешения тактирующим сигналом, что приведет к тому, что выход схемы насквозь просматривает вход в течении некоторого интервала времени.